MONDAY 15TH JUNE, 2009

THIS IS A COMPLETE AND UNMARKED TYPE 4B, HANDBOOK, THAT IS REQUIRED FOR THE DIGION SERVICE.

#### INDEX BY SECTIONS.

| SECTION 1  | INTRODUCTION                                         |

|------------|------------------------------------------------------|

| 1.1        | PURPOSE OF THE EQUIPMENT                             |

| 1.2        | GENERAL DESCRIPTION                                  |

| 1.2.1      | Ionogram Presentation                                |

| 1.2.2      | Removing Interfering Signals                         |

| 1.2.3      | Noise Interference Suppression                       |

| 1.2.4      | Date/Time/Ident. Numerals and Graticule              |

| 1.2.5      | Frequency Generation                                 |

| 1.2.6      | The Receiver                                         |

| 1.2.7      | The Transmitter                                      |

| 1.2.8      | Monitor and Recording CRT's                          |

| 1.3        | GENERAL SPECIFICATIONS                               |

| <u>1.4</u> | THE ANTENNA SYSTEM                                   |

|            |                                                      |

| SECTION 2  | SET-UP PROCEDURES                                    |

| 2.1.1      | Introduction                                         |

| 2.1.2      | Setting up the CRT Displays                          |

| 2.1.3      | Setting the Clock                                    |

| SECTION 3  | CIRCUIT DESCRIPTIONS                                 |

| 3.1        | THE CLOCK                                            |

| 3.1.1      | Overall Description                                  |

| 3.1.2      | Circuit Descriptions                                 |

| 3.1.3      | The Master Oscillator-Divider                        |

| 3.1.4      | Deleted                                              |

| 3.1.5      | THE OPERATIONAL CLOCK                                |

| 3.1.6      | The Primary and Secondary Dividers                   |

| 3.1.7      | The Operational Dividers                             |

| 3.1.8      | Additional Outputs and Circuitry                     |

| 3.1.9      | -                                                    |

| J/         | The Graticule Generator                              |

| 3.1.10     | The Graticule Generator The Transmit Pulse Generator |

| 3.1.12     | The Camera Drive Generator               |

|------------|------------------------------------------|

| 3.1.13     | THE CHRONOMETER                          |

| 3.1.14     | The Seconds Dividers                     |

| 3.1.15     | Seconds Dividers Auxiliary Outputs       |

| 3.1.16     | Chronometer Dividers Output Multiplexing |

| 3.1.17     | The Minutes Dividers                     |

| 3.1.18     | The 'Advance Count' Circuit              |

| 3.1.19     | Program Decoding Circuitry               |

| 3.1.20     | The Hours Dividers                       |

| 3.1.21     | The Days Dividers                        |

| 3.1.22     | The Years Dividers                       |

| 3.2        | FREQUENCY SYNTHESIZER                    |

| 3.2.1      | Introduction                             |

| 3.2.2      | Brief Description                        |

| 3.2.3      | THE DIGITAL SECTION                      |

| 3.2.4      | The Octave Divider                       |

| 3.2.5      | Programmable Divider A                   |

| 3.2.6      | Programmable Divider B                   |

| 3.2.7      | The Digital Comparator                   |

| 3.2.8      | THE RF SECTION                           |

| 3.2.9      | The VFO and Steering Circuitry           |

| 3.2.10     | 70MHz Oscillator and Mixer               |

| 3.2.11     | The Digital Interface Circuit            |

| 3.2.12     | The Pulse Modulator                      |

| 3.2.13     | The Reference Oscillator                 |

| <u>3.3</u> | TRANSMITTER                              |

| 3.3.1      | Brief Summary                            |

| 3.3.2      | The Power Supply                         |

| 3.3.3      | The Pulser                               |

| 3.3.4      | The Driver                               |

| 3.3.5      | The Power Amplifier                      |

| 3.3.6      | The Transmitter Fail Detector            |

| 3.4        | RECEIVER                                 |

| 3.4.1      | Brief Description                        |

| 3.4.2      | The Front End                            |

|            |                                          |

The First IF and Second Mixer

3.4.3

| 3.4.4      | The Second IF and Third Mixer                                                                         |

|------------|-------------------------------------------------------------------------------------------------------|

| 3.4.5      | The Third IF and Detector                                                                             |

| 3.4.6      | The Video Output and AGC Circuitry                                                                    |

| 3.5        | SIGNAL PROCESSING                                                                                     |

| 3.5.1      | Introduction                                                                                          |

| 3.5.2      | Blanking the First 50 km                                                                              |

| 3.5.3      | Noise Interference Suppression                                                                        |

| <u>3.6</u> | NUMERAL GENERATION                                                                                    |

| 3.6.1      | Introduction                                                                                          |

| 3.6.2      | The Numeral Generator                                                                                 |

| 3.6.3      | Generating the 'Greater than Four-Segment Numerals'                                                   |

| 3.6.4      | Generating the 'Less than Four-Segment Numerals'                                                      |

| 3.6.5      | The Commutation Circuitry                                                                             |

| 3.6.6      | The Commutation Generator                                                                             |

| 3.6.7      | The Master Commutation Circuit                                                                        |

| 3.7        | CONTROL SYSTEM                                                                                        |

| 3.7.1      | Brief Summary                                                                                         |

| 3.7.2      | Description of the Control Curcuitry on the Program Unit                                              |

| 3.7.3      | Programmed Soundings                                                                                  |

| 3.7.4      | Single Soundings                                                                                      |

| 3.7.5      | Camera Drive Control                                                                                  |

| 3.7.6      | Numeral Indication Display Control                                                                    |

| 3.7.7      | A-Scan Display Control                                                                                |

| 3.7.8      | The Control Logic A3A8                                                                                |

| 3.7.9      | Video Control Logic                                                                                   |

| 3.7.10     | Numeral Indicator Control Logic                                                                       |

| 3.7.11     | The Transmitter Control Logic                                                                         |

| 3.7.12     | The X-Blank Generator                                                                                 |

| 3.7.13     | Control of the Transmitter Power Supply Drive,<br>Transmit Pulse Gate and Transmit Fail Warning Logic |

| 3.7.14     | The Transmitter Power Supply Drive Circuit                                                            |

| 3.7.15     | The Transmit Pulse Gate                                                                               |

| 3.7.16     | The Transmit Fail Warning Circuitry                                                                   |

| 3.7.17     | Ancilliary Circuitry                                                                                  |

| 3.7.18     | The X-NI Reset Circuit                                                                                |

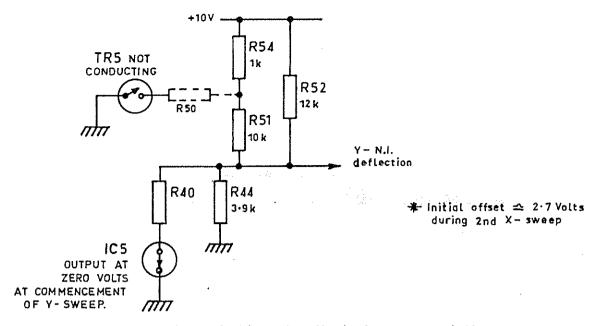

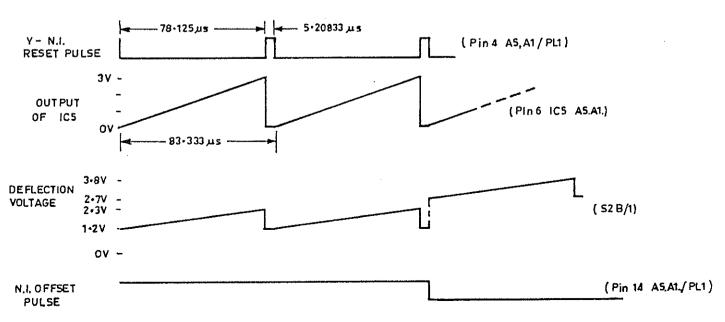

| 3.7.19     | The Y-NI Reset Circuit                                                                                |

| 3.7.20     | Set-Up Z-Modulation Circuit                                                                           |

erente

3000E

entrole.

viing

spipesh

1-11/10

polytim

| <u>3.8</u>  | DISPLAY SYSTEM                                  |

|-------------|-------------------------------------------------|

| 3.8.1       | Brief Summary                                   |

| 3.8.2       | Main and Monitor Display Assemblies             |

| 3.8.3       | The 18 Volt Regulator                           |

| 3.8.4       | The Power Supply Assembly                       |

| 3.8.5       | The EHT Divider Assembly                        |

| 3.8.6       | The Deflection Circuits                         |

| 3.8.7       | Z-Modulation Circuit                            |

| 3.8.8       | THE TIMEBASES                                   |

| 3.8.9       | The Miller Intergrator Timebase Circuit         |

| 3.8.10      | The Ionogram Timebases, X Main and Y Main       |

| 3.8.11      | The A-Scan Timebase and Blanking Circuitry      |

| 3.8.12      | THE NUMERAL INDICATION TIMEBASES                |

| 3.8.13      | Summary of Numeral Indication Display           |

| 3.8.14      | The NI Display Deflection Sequences             |

| 3.8.15      | The NI Timebases, X NI and Y NI                 |

| 3.8.16      | THE SET-UP DISPLAY                              |

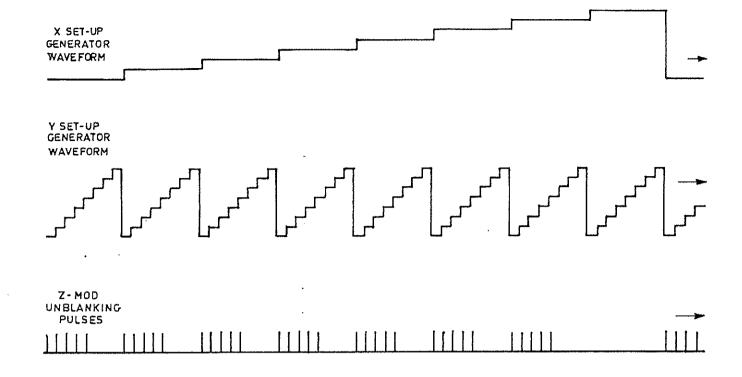

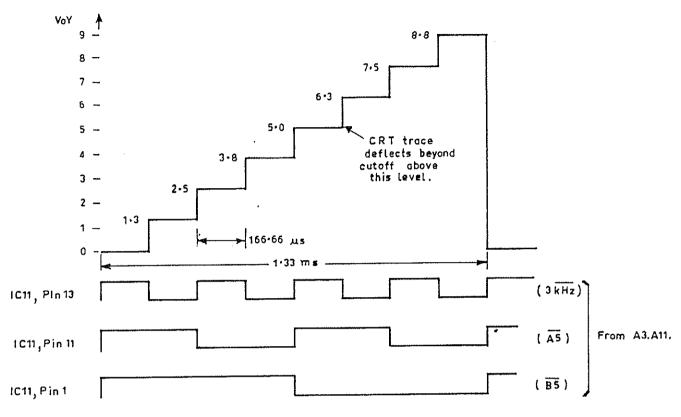

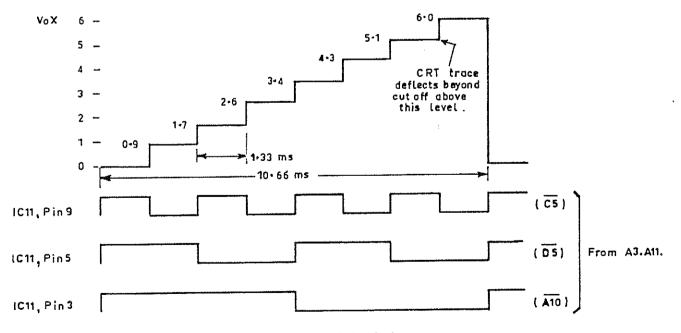

| 3.8.17      | The Staircase Generators, X SET-UP and Y SET-UP |

|             |                                                 |

| 3.9         | THE CAMERA                                      |

| 3.9.1       | Brief Description                               |

| 3.9.2       | The Camera Motor Drive Circuit                  |

|             |                                                 |

| 3.10        | POWER SUPPLIES                                  |

| 3.10.1      | Introduction                                    |

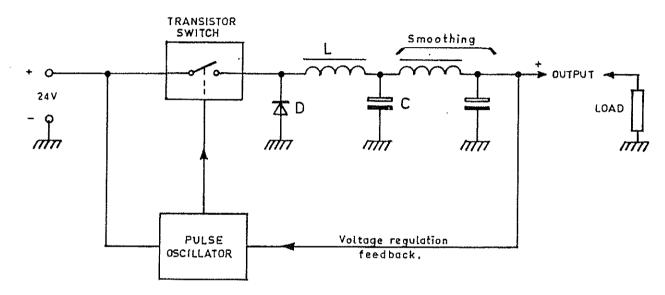

| 3.10.2      | The Main Power Supply/Battery Charger           |

| 3.10.3      | Voltage Regulation                              |

| 3.10.4      | Current Limiting                                |

| 3.10.5      | The IC Power Supply                             |

| 3.10.6      | The IC Regulators                               |

| <u>3.11</u> | PRESET PROGRAMME                                |

(Board not supplied with standard ionosonde)

#### INDEX BY ASSEMBLIES

| UNIT                 | ASSEMBLY                             | RELEVANT SECTION PARAGRAPHS                                       |

|----------------------|--------------------------------------|-------------------------------------------------------------------|

| Al MAIN POWER SUPPLY | Alal/Ala2                            | 3.10.1. to 3.10.4                                                 |

| A2 BATTERY           |                                      | •                                                                 |

| A3 CLOCK             | A3A1 YEARS                           | 3.1.1, 3.1.22, 3.1.16, 3.1.18.                                    |

|                      | A3A2 DAYS                            | ", 3.1.21, ", ".                                                  |

|                      | A3A3 HOURS                           | т , 3.1.20,  п  ,  п  .                                           |

|                      | A3A4 NUMERAL GENERATOR               | 3.6.1 to 3.6.4                                                    |

|                      | A3A5 SECONDS                         | 3.1.1, 3.1.14, 3.1.15, 3.1.16, 3.6.5, 3.6.6, 3.7.20.              |

|                      | A3A6 STN No./MASTER CON              | M.                                                                |

|                      |                                      | 3.6.1, 3.6.5, 3.6.7.                                              |

|                      | A3A7 MINUTES                         | 3.1.1, 3.1.17, 3.1.18, 3.1.19, 3.6.5.                             |

|                      | A3A8 CONTROL LOGIC                   | 3.7.1, 3.7.8 to 3.7.16.                                           |

|                      | A3A9 PRESET PROGRAM                  |                                                                   |

|                      | A3A10 COMM. GENERATOR                | 3.6.1, 3.6.5, 3.6.6, 3.7.18.                                      |

|                      | A3ALL OP'N'L DIVS,<br>GRATICULE GEN. | 3.1.1, 3.1.5, 3.1.7 to 3.1.12.                                    |

|                      | A3A12 CLOCK OSCILLATOR               | 3.1.1, 3.1.3, 3.1.4, 3.5.1, 3.5.2, 3.5.3, 3.7.20, 3.8.16, 3.8.17. |

| A4 SYNTHESIZER       | A4Al DIGITAL SECTION                 |                                                                   |

|                      | A4A2 RF SECTION                      |                                                                   |

| A5 PROGRAM           | A5A1 TIMEBASES/FUNCTION<br>CONTROLS  | 3.7.1, 3.7.2 to 3.7.7, 3.8.8 to 3.8.15.                           |

| A6 TRANSMITTER       | A6Al POWER SUPPLY/PULSE              | R 3.3.1, 3.3.2, 3.3.3.                                            |

|                      | A6A2 DRIVER                          | 3.3.1, 3.3.4.                                                     |

|                      | A6A3 POWER AMPLIFIER                 | 3.3.1, 3.3.5.                                                     |

|                      | A6A4 Tx TAIL DETECTOR                | 3.3.1, 3.3.6.                                                     |

| A7 RECEIVER          | A7A1 BANDPASS FILTER                 | 3.4.1, 3.4.2.                                                     |

|                      | A7A2 VFO AMP./lst MIXER              |                                                                   |

|                      |                                      | 3.4.1, 3.4.3.                                                     |

|                      | A7A5 lst IF/2nd MIXER & OSC.         | 3.4.1, 3.4.3.                                                     |

|                      | A7A6 2nd IF/3rd MIXER & OSC.         | 3.4.1, 3.4.4.                                                     |

provide -

A7A7 3rd IF/DETECTOR 3.4.1, 3.4.5. A7A8 AGC & PULSE SHAPING 3.4.1, 3.4.6.

A8 MAIN DIAPLAY

A8Al 18V REGULATOR

3.8.1, 3.8.2, 3.8.3.

A8A2 POWER SUPPLY

3.8.1, 3.8.2, 3.8.4.

A8A3 EHT DIVIDER

3.8.1, 3.8.2, 3.8.5.

A8A4 DEFLECTION CIRCUIT 3.8.1, 3.8.2, 3.8.6.

A8A5 Z MODULATION CCT. 3.8.1, 3.8.2, 3.8.7.

A9 CAMERA

A9Al MOTOR DRIVE CCT.

3.9.1, 3.9.2.

Alo MONITOR DISPLAY

AS FOR A8

All CABINET

Al2 IC POWER SUPPLY

Al2Al IC POWER SUPPLY

3.10.1, 3.10.5.

Al2A2 REFULATORS

3.10.1, 3.10.6.

Al3 HARNESS

# SECTION 1

### INTRODUCTION

| Par. No. | Title                                   |

|----------|-----------------------------------------|

| 1.1      | PURPOSE OF THE EQUIPMENT                |

| 1.2      | GENERAL DESCRIPTION                     |

| 1.2.1    | Ionogram Presentation                   |

| 1.2.2    | Removing Interfering Signals            |

| 1.2.3    | Noise Interference Suppression          |

| 1.2.4    | Date/Time/Ident. Numerals and Graticule |

| 1.2.5    | Frequency Generation                    |

| 1.2.6    | The Receiver                            |

| 1.2.7    | The Transmitter                         |

| 1.2.8    | Monitor and Recording CRT's             |

| 1.3      | GENERAL SPECIFICATIONS                  |

| 1.4      | The Antenna System                      |

#### 1.1 PURPOSE OF THE EQUIPMENT

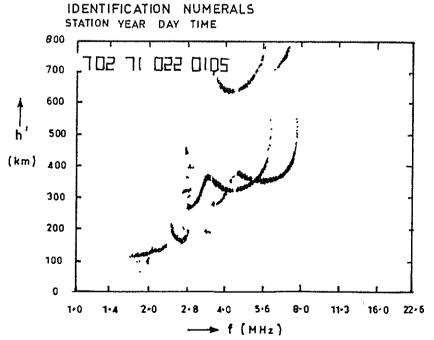

The general purpose of this equipment is to sound the ionosphere at regular intervals by the pulse-echo technique at vertical incidence, and to plot the relationship of the virtual height of reflection of the pulse echoes against the transmitted frequency.

The operating frequency of a pulsed transmitter is varied over the range 1 MHz to 22.6 MHz. The resulting echoes from the ionosphere are then detected by a receiver tuned, automatically, to the same frequency as the transmitter. The echoes received are processed to remove noise and interference and are displayed on a cathode ray tube along with a graticule indicating virtual height along one axis and frequency along the other. The trace is then photographed by an automatically operated camera, and the records produced are called ionograms. From these records the necessary ionospheric data are obtained and used for prediction and research purposes.

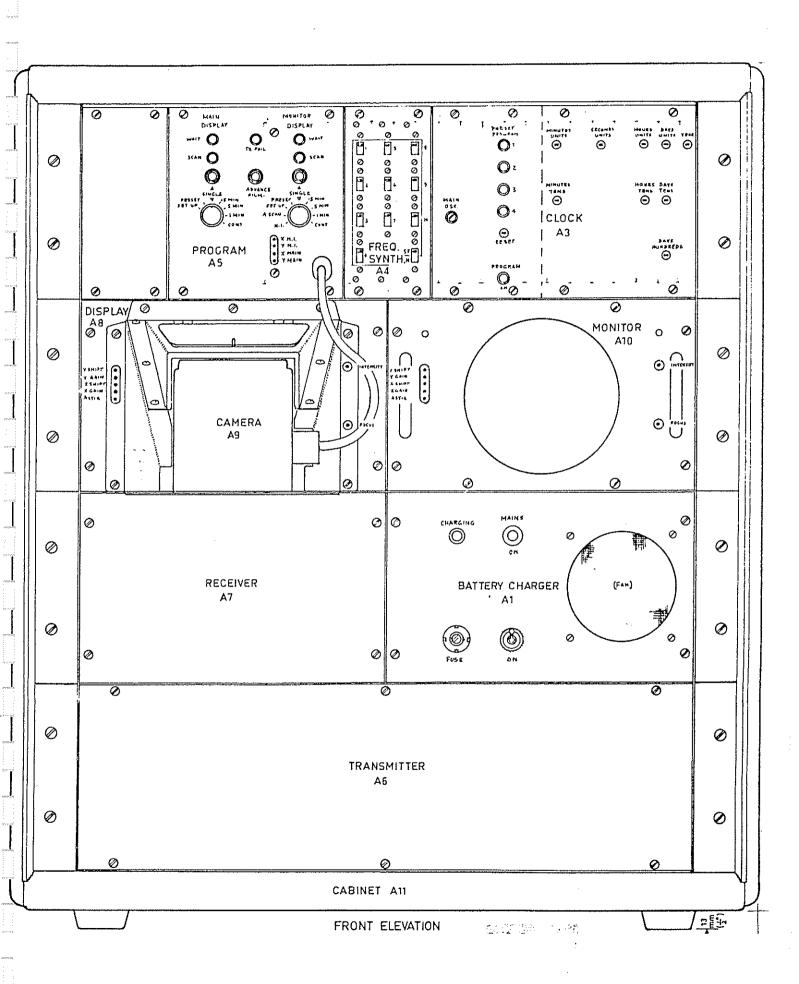

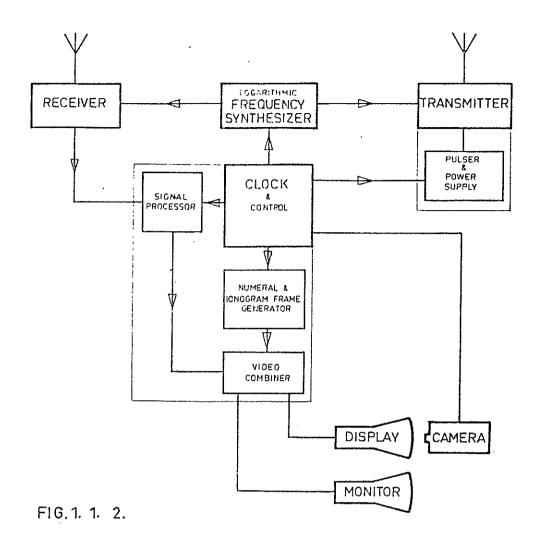

The style of ionogram produced by the 4A ionosonde is illustrated in figure 1.1.1. A simplified block diagram is given in figure 1.1.2.

#### 1.2 GENERAL DESCRIPTION

This instrument is a largely solid state, swept-frequency, pulse ionosonde designed for routine vertical-incidence sounding of the ionosphere. It employs a digital frequency synthesizer and digital programming, control, signal processing and display techniques with an absolute minimum of electromechanical components to ensure high reliability and provide the possibility of remote, unattended operation.

Only six vacuum tube devices are used in the instrument. Four valves are employed in the transmitter final power amplifier, producing 5 kW peak pulse-power output. Two conventional CRT's are employed in the recording and monitor displays.

The digital frequency synthesizer provides coverage from 1 MHz to 22.6 MHz in 576 logarithmic steps. A complete frequency sweep to produce an ionogram takes 12 seconds of a 20 second program cycle. A group of front panel switches allows the operator to manually select any of the synthesizer's 576 channels so that single frequency soundings can be made in conjunction with the A-scan display facility. It is an entirely electronic frequency control system.

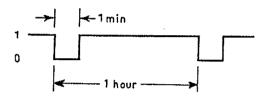

The instrument features selectable programming, there being four basic programs. These range from one sounding every 15 minutes ('normal' programming) to three per minute ('continuous'). An optional 'preset programmer' can be set to vary the selected program for chosen periods in twenty four hours. The programming and control is derived from a crystal-controlled chronometer, which also provides a digital date/time output for recording on the ionogram and which may be displayed on the monitor CRT for the operator's convenience. The numerals are 8-segment, rather than 7-segment, characters to improve clarity.

Signal processing of the received echoes is employed to remove noise and interference from the ionogram. The ionogram is uncluttered by bands of noise or interference from HF transmissions, reducing uncertainties and ambiguities in interpretation and scaling.

The ionogram is recorded on 16 mm film. Consumption is 750 mm per day when normally programmed at four soundings per hour. The recorded ionogram is orietated such that the film can be projected by a standard 16 mm movie projector providing a speeded-up, time-lapse view of the ionosphere. The use of a CRT having a small spot size and a low distortion optical system provides more than adequate scaling accuracy.

Power consumption is about 100 watts, derived from a mains-operated power supply. In the event of mains failure two 40 amp-hour lead-acid batteries may provide power for periods up to 10 hours. The batteries are charge-maintained from the mains power supply.

Standard ISEP rack and cabinet mechanical components are widely used throughout the ionosonde assembly, standardising mechanical components and simplifying construction. The overall size, together with a weight less than 60 kg, allows bench mounting.

Digital circuitry throughout the instrument is all commonly available TTL logic.

Two prime design objectives of this instrument were simplified, reliable routine operation and improved date retreival. To this end, the electronics have been designed to provide easy setting-up and simple, but flexible program selection and operation with a range of useful alternatives. Also, the ionogram format and recording have been designed to reduce film usage and processing and greatly improve the speed and ease of extracting data.

#### 1.2.1 Ionogram Presentation

The method of producing the ionogram, and its format, differ from previous practice and techniques.

Traditionally, an ionogram was produced by drawing film past an intensity-modulated CRT display having range (i.e. virtual height) along the timebase and the return echo pulses blanking the trace at the suitable intervals. Frequency marks were obtained by momentarily blanking the whole trace as the VFO passed frequency markers, usually at 1 MHz intervals, derived from a crystal oscillator and harmonic generator. Date, time and station identification were recorded on the film by momentarily flashing lamps to illuminate the date/time wheels of an electromechanical clock device.

In the 4A ionosonde, the ionogram is slowly 'written' on the face of the CRT by a scanning process, in a similar manner to the way a TV picture is scanned across a picture tube. The line scan goes from 0 to 800 km and moves along the frame, from left to right, with increasing frequency. The complete ionogram, including the graticule and numerals, is written on the CRT while the camera shutter remains open and the film stationary. The film is advanced after the shutter has closed. The received echoes are prevented from being superimposed on the graticule or numerals to avoid ambiguity or confusion.

#### 1.2.2 Removing Interfering Signals

Interference from HF transmissions is prevented from being displayed in the following way. The receiver AGC circuit samples the level of signals received, in the particular frequency channel, following each transmit pulse and adjusts the receiver gain accordingly. If the echo pulses, or any other pulse-type interference, exceeds this level by a small threshold they are detected and converted to a digital-level pulse for processing by the signal processor. If the echoes do not exceed the level of received signals then nothing will be displayed on the CRT, leaving a small hole in the ionogram. Very little information is lost as interference has to spread over a wide frequency band before large holes become apparent in the recorded trace.

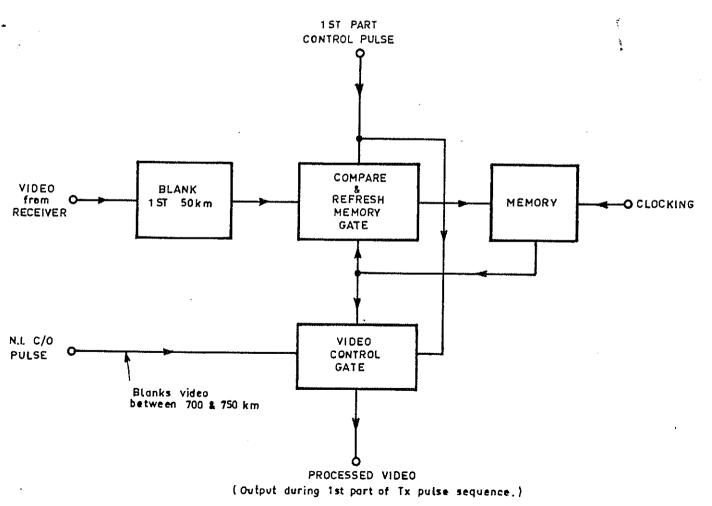

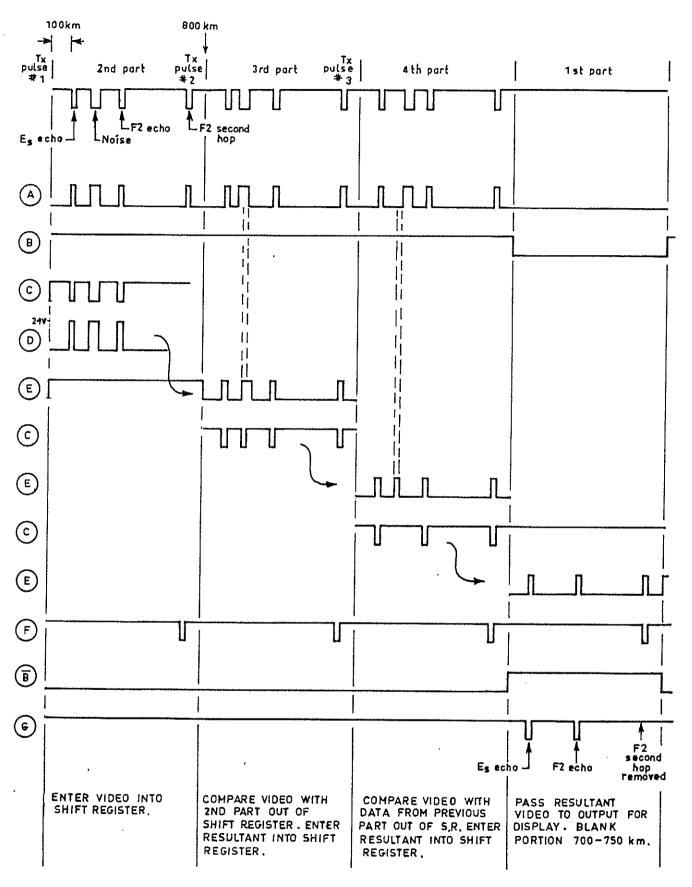

The signal processor first blanks all signals in the first 50 km of the ionogram, removing the ground pulse. As the graticule and the transmit pulse are derived from the same circuitry in the ionosonde, displaying the ground pulse is unnecessary.

#### 1.2.3 Noise Interference Suppression

Atmospheric static is essentially random in nature and ignition noise, while repetitive, does not exhibit a stable interval between pulses. The repetitive characteristics of the received pulses are used to exclude noise and pulse-type interference from the ionogram.

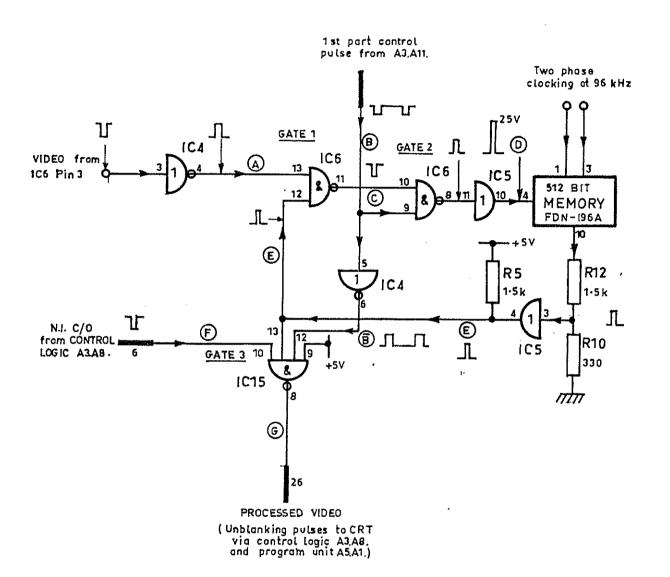

Three RF pulses are transmitted on each frequency channel. The detected first echoes and noise are stored in a shift register and then compared with echoes from the second transmitted pulse along with noise and any spurious pulses. Any coincident pulses, predominantly echoes, are recirculated into the shift register and the comparison repeated following the third transmitted pulse. At the end of this cycle, echoes, most likely being the only coincident events, are virtually the only surviving signals and are subsequently displayed on the CRT.

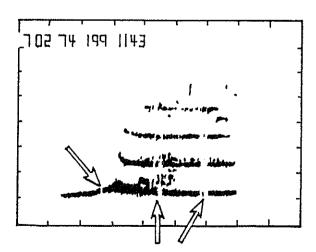

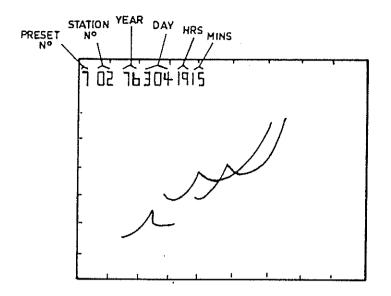

FIG. 1. 2.1. lonogram, showing holes produced by AGC operation under conditions of severe interference.

FIG. 1. 1. Style of lonogram produced by 4A 'Sonde.

#### 1.2.4 Date/Time/Ident. Numerals and Graticule

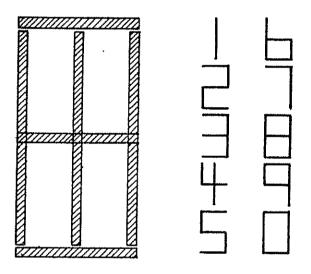

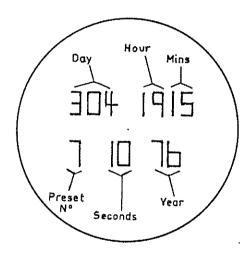

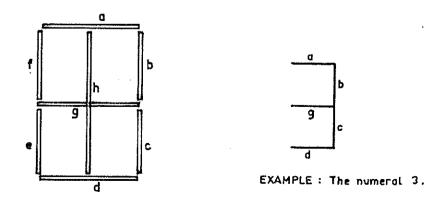

The numerals are produced by digital techniques, eight-segment characters being used. Improved clarity over seven-segment characters is obtained. The appearance of the numerals is illustrated in fig. 1.2.2.

Three identification numerals are provided. The last two digits of the year, a three digit day number, and four digit hours/minutes numbers are displayed on the ionogram.

FIG. 1. 2. 2. Arrangement of 8-Segment Numerals

The graticule is also digitally produced. The range and frequency timebases are synchronised from the same source that produces the graticule brightening pulses, and the transmit pulses.

Height markers are at 100 km intervals to 800 km, the maximum range of the instrument. Frequency markers are derived from the chronometer dividers and not by comparing a wideband frequency comb with the transmit frequency. Frequency markers are at even intervals along the frequency axis, there being ten all told, at 1.0, 1.4, 2.0, 2.8, 4.0, 5.6, 8.0, 11.3, 16.0 and 22.6 MHz. The edges of the graticule indicate the 1.0 MHz and 22.6 MHz markers.

#### 1.2.5 Frequency Generation

The frequency synthesizer is controlled by a 10-bit binary number which steps the output through 576 channels increasing logarithmically in frequency with each step. The synthesizer may be manually set to any of the 576 channels by a group of ten front panel switches for single-frequency soundings.

The synthesizer provides two outputs, one to drive the transmitter and one as the first conversion signal for the receiver.

#### 1.2.6 The Receiver

The receiver is a triple-conversion design employing IF's of 70 MHz, 10.7 MHz and 1.6 MHz. The receiver bandwidth of 40 kHz is obtained in the 1.6 MHz IF stage which employs L-C circuits to achieve the narrow bandwidth with steep skirt selectivity. Overall gain is about 90 dB. Double-balanced ring-diode mixers are employed for their large signal-handling characteristics and to reduce spurious responses. No RF amplification is employed, the antenna signals are fed to the first mixer via a bandpass filter consisting of a low-pass filter with a cutoff of 1.6 MHz and a high-pass filter with a cutoff of 23 MHz. Both cutoff frequencies can be varied. The low-pass filter attenuates possible strong local AM broadcast band transmitters which may cause receiver overload and cross-modulation of signals above the cutoff frequency. The high-pass filter attenuates upper-HF and VHF transmissions that may also cause cross modulation or breakthrough into the first IF.

#### 1.2.7 The Transmitter

The transmitter employs a solid-state, pulsed, wideband amplifier to drive the power amplifier. The PA employs four tubes which were designed for TV vertical output stages. This allows a low EHT to be used and 1.5 kV is supplied to the anodes, the screens being pulsed with a 500 V, 40  $\mu s$  pulse in synchronism with the driver.

The peak pulse-power output is 5 kW which falls to about 1 kW near 12MHz and about 500 W above 20 MHz.

#### 1.2.8 Monitor and Recording CRT's

The monitor and recording CRT's are electrically identical, and mechanically interchangeable. The recording CRT however, is rotated 90° to the monitor so that the ionogram is correctly orientated on the film. Operationally the two units are independent. They can be individually programmed to perform separate individual functions.

The programming functions are selected by front panel switches. The recording CRT has seven programmable functions and the monitor, nine. The seven functions for the recording CRT are also common to the monitor.

The seven common functions are as follows:

SET UP: A 5  $\times$  7 dot matrix is displayed on the CRT to

facilitate the adjustment of CRT brightness,

focus and geometry as well as camera

focussing.

PRESET: This initiates the Preset Programmer.

SINGLE: A single ionogram can be produced by pressing

a push button on the front panel.

15 MIN: 'Normal' programming. The ionosonde will

automatically make a sounding every 15

minutes.

5 MIN:

The ionosonde will automatically make a

sounding every five minutes.

1 MIN:

The ionosonde will automatically make a

sounding every minute.

CONT .:

'Continuous' sounding. As the complete

sounding cycle lasts 20 seconds, the ionosonde

will record three ionograms per minute.

The two functions unique to the monitor are:

N.I.:

'Numeral Indication'. The date and time are displayed, in large format digital numerals, on the monitor CRT. The seconds are also included in this display. This facility enables operator to 'set' the clock.

A-SCAN:

A standard A-scan is displayed each program-

med sounding.

It is possible for a second camera to be mounted on the monitor unit and two separate, independently programmed recordings to be made simultaneously.

#### 1.3 GENERAL SPECIFICATIONS

Frequency Range

Frequency Generation Digital Synthesizer

Number of Channels 576

Frequency Sweep Configuration Logarithmic

Frequency Sweep Time 12 seconds

Transmitter Pulse Power Output 5 kW

Transmitter Pulse Width 41.67 µs

Pulse Interval 5.33 ms, three on each frequency channel

1 to 22.6 MHz

Maximum Virtual Height Range 800 km

Height Marker Interval 100 km

Frequency Markers Ten equally spaced markers at 1.0, 1.4,

2.0, 2.8, 4.0, 5.6, 8.0, 11.3, 16.0, 22.6 MHz

22.0 M

Date/Time/Ident 8-segment digital numerals written on ionogram.

Programming Four manually selected automatic

programs: l each 15 min.

l each 5 min.

l each 1 min.

and 3 per min.

Optional 'preset programmer' can provide selectable variation of normal program.

Film 16 mm

Film consumption 750 mm per day at four soundings

per hour

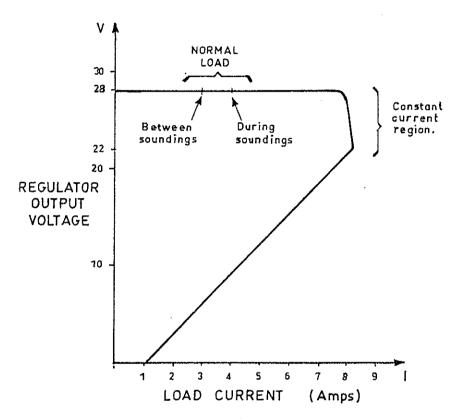

Power Supply Mains operated, or 22 to 28V @ 4A max.

from two lead-acid batteries

Size H = 609 mm, W = 520 mm, D = 457 mm

Weight 52 kg

#### 1.4 The Antenna System

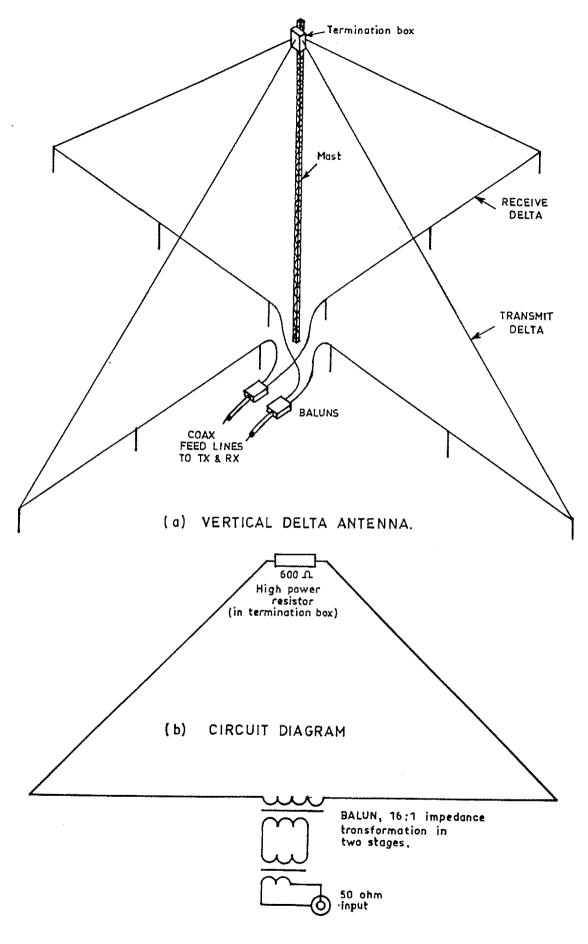

Two Vertical Delta antennas are usually employed, one for the transmitter and one for the receiver. The configuration is shown in figure 1.4.1. Each antenna consists of a large, triangular loop of wire, supported at the apex. The two antennas are mounted orthogonally to reduce coupling between them. The feedpoint is at the centre of the base of the loop. A 600 ohm terminating resistor is inserted in series with the loop at the apex so that the antenna provides essentially unidirectional radiation in the vertical direction. A high power terminating resistor is necessary for the transmitting antenna.

These antennas are used because they may be erected from a single tower, are low in cost, provide an essentially vertical radiation pattern and have reasonable radiation efficiency over the frequency range.

The 4A Ionosonde is designed for low impedance, unbalanced receiver input and transmitter output and employs coaxial cable feedlines to each antenna. This is to avoid problems with transmitter feedline radiation being coupled back into the receiver and digital circuitry in the instrument, which is susceptible to RF interference. It also reduces interaction between the two feedlines, particularly on long runs. Coaxial cable feedlines may be conveniently buried.

The Vertical Delta antenna has an average feedpoint impedance of about 800 ohms and requires a balanced feedline. A balun transformer is used to transform the antenna feedpoint impedance to 50 ohms for the coaxial cable feedline, and converts the unbalanced cable to a balanced configuration to suit the antenna feedpoint characteristics. The balun is located at the antenna and has a turns ratio of 4:1 providing an impedance ratio of 16:1. Essentially, it consists of two transmission line transformers, each wound on several large toroidal ferrite cores, to obtain wide bandwidth, the impedance transformation being obtained in two steps.

FIG. 1. 4.1.

# SECTION 2

### SET-UP PROCEDURE

| Par. No. | <u>Title</u>                |

|----------|-----------------------------|

| 2.1.1    | Introduction                |

| 2.1.2    | Setting up the CRT Displays |

| 2 7 3    | Setting the Clock           |

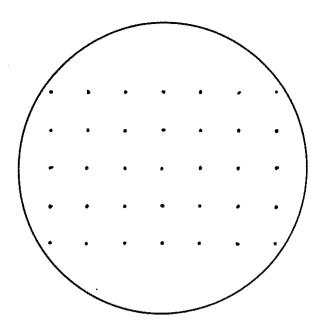

FIG. 2.1.1. The SET-UP graticule adjusted for the best size.

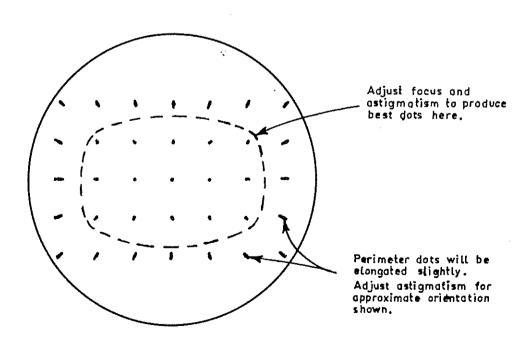

FIG. 2.1.2. The SET-UP graticule adjusted for the optimum focus and astigmatism. Intensity should be kept low. (Elongation of dots exaggerated.)

#### 2.1 <u>SET-UP PROCEDURES</u>

#### 2.1.1 Introduction

Each ionosonde is completely aligned and set-up ready for operation prior to commissioning. Initially however, the date and time will need to be set and some of the preset controls may be adjusted to suit the individual preferences of the operator. In addition, the preset controls may need to be adjusted after an initial "settling" period, following servicing, or when putting a sonde back into regular operation following a period of disuse.

This section only includes the setting of these preset controls accessible from the front panels of the various units.

#### 2.1.2 Setting up the CRT Displays

- (1) Turn on the Main Power Supply (Al) and allow 10-15 minutes for the instrument to warm up.

- (2) Remove the film magazine from the camera.

- (3) Set both display function switches (on the front panel of the PROGRAM unit) to SET-UP.

- (4) Adjust intensity and focus on each CRT to obtain a reasonably clear pattern. This is only a rough, initial adjustment.

- (5) Adjust the Y-shift and gain, and the X-shift and gain controls on each Display unit in turn so that the whole dot matrix is squarely positioned and not overscanned. See figure 2.1.1. Note that the Main Display CRT is rotated 90° with respect to the MONITOR CRT.

- (6) Adjust the intensity, focus and astigmatism controls to obtain small, well-focussed inner dots. The size of the dots is determined by the brightness. The finest dots are obtained at a low intensity. The dots around the perimeter may be slightly elliptical, especially the four corner dots. Adjustment of the astigmatism control will rotate the elongated dots. Set this control so that the dots appear similar to the exaggerated display illustrated in figure 2.1.2.

- (7) Set the MONITOR function switch to N.I. Adjust the X-NI and Y-NI trimpots for the desired display size. These controls are accessible from the PROGRAM unit front panels.

- (8) Set both function switches to SINGLE. Set the TX STOP switch to the UP position (off). This is a slide switch (Al3Al.Sl) located on the harness channel (see dwg: MD-72Yl), at the right-hand side, opposite the battery input connector. This prevents the Transmitter being pulsed during testing.

- (9) Press the SINGLE pushbutton for the MONITOR to initiate a single ionogram. The following sequence of events should occur:

- a) The Monitor WAIT light comes on.

- b) A short time later the Monitor SCAN light comes on and a sounding commences.

- c) About two seconds later the ionogram will commence at the left hand side of the Monitor CRT screen.

- d) At the end of the sounding cycle the SCAN light extinguishes.

- (10) Check that the ionogram size is adequate, not overscanned, and that it does not commence or finish partially off-screen. If the ionogram is the incorrect size, adjust the X-MAIN and Y-MAIN timebase controls on the Program unit front panel.

- (11) Repeat (9) and (10) for the MAIN display. The ionogram size should be sufficient to fill the film frame. Adjust the shift and gain controls if necessary to adjust the ionogram size and position. The best definition for film recording is obtained with minimal brightness and a wide lens aperture.

- (12) Check that all programmed soundings operate for both the MAIN and MONITOR displays.

- (13) Connect the antennas and set the TX STOP switch to the DOWN position to allow the transmitter to be pulsed during a sounding.

- (14) Set the function switches to SINGLE and initiate a sounding. Alternatively, set the switches to CONTINUOUS.

- (15) Observe the ionogram and see that the date/time/ident numerals are being displayed and that reflections are obtained. See that the graticule is not affected by RF interference. If so, check all the earth bonding to the harness channel, particularly to the Receiver and Transmitter chassis and the Synthesizer cables.

- (16) Set the Monitor function switch to A-Scan. Initiate a sounding from the Main function switch and observe the A-Scan. Echoes should be readily visible. The A-Scan sweep width can be adjusted if necessary. See section 3.8.11.

- (17) Set Main function switch to desired program and return Monitor function switch to SINGLE.

#### 2.1.3 Setting the Clock

The timing of all the ionosonde functions is derived from a crystal-controlled master oscillator. This is adjusted by a trimmer which is accessible through the front panel. It is designated MAIN OSC. and is mounted on board A3A12, located immediately to the right of the Frequency Synthesizer.

The frequency of the master oscillator should be checked using a digital frequency meter (d.f.m.). Measure the frequency at pin 14 of IC2 on board A3A12 (dwg: CD-229Y1). It should be set to within 100 Hz of 6144 kHz. The d.f.m. should be warmed-up for at least one hour beforehand. Note which direction the trimmer is turned to increase or decrease the frequency.

Having set the master oscillator, the chronometer section of the ionosonde clock needs to be set to the station time, together with the day number and year, and the clock synchronised to UT.

Set the MONITOR function switch to N.I. Each of the displayed chronometer numbers can be set by operating the microswitches accessible through the front panel of the clock section of the top rack assembly. Set the numerals in the following order:-

MINUTES UNITS)

Set about 3 mins. ahead of required time

HOURS UNITS

HOURS TENS

DAYS UNITS

DAYS TENS

DAYS HUNDREDS

YEAR UNITS

When this is completed, watch the seconds numerals on the N.I. display and depress the SECONDS microswitch, holding it operated, immediately a "OO" is displayed. This stops the clock at the beginning of the minute displayed at that time. It should be by now a minute or so ahead of the correct station time. To synchronise the clock, monitor a standard time signal transmission. When the displayed minute is reached, as indicated by the time signal transmission, release the SECONDS microswitch at the OO second indicated by the time transmission identification. The ionosonde clock is then synchronised to UT.

If the master oscillator is not within a very close tolerance of the frequency, then a cumulative time error will become apparent. Check the ionosonde time against the time signal transmission each day for a number of days following setting of the clock. If the master oscillator is a little high in frequency the clock will be slightly fast. If it is low, the clock will be slow. Reset the clock, then adjust the MAIN OSC. trimmer slightly to compensate. Monitor the clock time over the next week to determine the effect. Make further adjustments as necessary.

## SECTION 3

### CIRCUIT DESCRIPTIONS

# 3.1 CLOCK

| <u>Par. No</u> . | <u>Title</u>                                                | Drawing No.      |

|------------------|-------------------------------------------------------------|------------------|

| 3.1.1            | Overall Description                                         | CB-34Yl          |

| 3.1.2            | Circuit Descriptions                                        |                  |

| 3.1.3            | The Master Oscillator-Divider                               | CD-229Yl (A3Al2) |

| 3.1.4            | Generating the Clock Pulses For the Signal Processor Memory | ff ff f9         |

| 3.1.5            | THE OPERATIONAL CLOCK                                       | CB-34Yl          |

| 3.1.6            | The Primary and Secondary Dividers (on A3A5)                | CD-227Yl         |

| 3.1.7            | The Operational Dividers                                    | CD-225Yl (A3All) |

| 3.1.8            | Additional Outputs and Circuitry .                          |                  |

| 3.1.9            | The Graticule Generator                                     | CD-225Yl (A3All) |

| 3.1.10           | The Transmit Pulse Generator                                | tt tt tt         |

| 3.1.11           | The Y-Blank Generator                                       | ft ft ft         |

| 3.1.12           | The Camera Drive Generator                                  | n n n            |

| 3.1.13           | THE CHRONOMETER                                             | CB-34Yl          |

| 3.1.14           | The Seconds Dividers                                        | CD-227Yl (A3A5)  |

| 3.1.15           | Seconds Dividers Auxiliary Outputs                          | 11 11 11         |

| 3.1.16           | Chronometer Dividers Output Multiplexing                    |                  |

| 3.1.17           | The Minutes Dividers                                        | CD-224Yl (A3A7)  |

| 3.1.18           | The 'Advance Count' Circuit                                 | tt tt tt         |

| 3.1.19           | Program Decoding Circuitry                                  | 11 11 11         |

| 3.1.20           | The Hours Dividers                                          | CD-221Yl (A3A3)  |

| 3.1.21           | The Days Dividers                                           | CD-220Yl (A3A2)  |

| 3.1.22           | The Years Dividers                                          | CD-218Yl (A3Al)  |

### 3.1.1 Overall description (Dwg: CB-34Y1)

The Ionosonde Clock times all the operations of the instrument including the programming, frequency synthesizer, transmitter, signal processing, display generation and camera operation. It also provides outputs for the generation of the date/time display on the MONITOR CRT (NI display) and on the recorded ionogram.

A complete block diagram is given in drawing CB-34Yl. There are three major sections to the clock, their titles and functions being as follows:

- (a) The MASTER OSCILLATOR/DIVIDER. This provides 96KHz (the PRIMARY FREQUENCY) to the PRIMARY DIVIDER and narrow, two-phase high frequency clock pulses for the operation of the SIGNAL PROCESSOR.

- (b) The OPERATIONAL CLOCK. This times all the operations of the ionosonde during a sounding as well as continuous functions such as the numeral generation and date/time display. It provides lpps to drive the CHRONOMETER and a number of binary coded outputs for the operation of the CONTROL SYSTEM, the FREQUENCY SYNTHESIZER during a frequency scan and the COMMUTATION GENERATOR for the generation of the date/time numeral display. In addition, this section of the clock generates:

- \* The transmit pulses

- \* A control pulse for the SIGNAL PROCESSOR shift register

- \* Camera motor drive pulses which also serve as the Y MAIN and X A-SCAN timebase reset waveform.

- \* Y-blanking pulses for the ionogram display

- \* The Graticule for the ionogram display

- \* Pulses for the generation of the X-Blank control and display pulse.

- (c) The CHRONOMETER. This derives five binary-coded outputs for the date/time display, provides outputs for the programming circuitry in the CONTROL SYSTEM and resets the OPERATIONAL CLOCK dividers every 20 seconds. In addition, it generates a pulse to close the camera shutter at the end of a sounding and pulses for the 'Tx-Fail' warning light.

#### 3.1.2 Circuit descriptions

With the exception of the Master Oscillator, the Clock uses digital TTL integrated circuits throughout. Seven plug-in printed circuit boards contain the complete Clock circuitary, these being sub-assemblies:

A3A1 A3A3 A3A5 A3A7 A3A11 A3A12

The block diagram in drawing CB-34Y1 indicates which sections of the Clock circuitry are located on each sub-assembly.

## 3.1.3 The Master Oscillator-Divider (on A3A12) (Dwg: CD-229Y1)

The Master Oscillator operates at 6144kHz and is divided by 64 to produce the 'Primary Frequency' of 96kHz.

Transistor TR1 is a crystal-controlled Colpitts oscillator. The 6144kHz crystal is adjusted precisely to frequency by a series trimmer capacitor, C2, which is accessible through the front panel. Transistor TR2 interfaces the oscillator output to TTL logic levels, also acting as a buffer. A crystal in the 6MHz frequency range is used owing to its superior temperature stability characteristics compared to lower frequency units.

The Master Osiclator output is first divided by 16 with IC2, a type 7493 binary divider, producing pulses 1.3 us wide which are subsequently used as clock pulses for the Signal Processor shift register or memory.

The output of IC2 is then divided by four in IC1, a 7493, using only two out of its four binary dividers. The output, 96kHz, goes to pin 27 of AeA12/PL1. This signal also clocks the shift register.

The Signal Processor Memory is a dynamic shift register, the operation of which requires clock pulses at a repetition rate of 96kHz to accommodate 512 bits of data in a 5.33mS period. Each data bit occupies 10.4 uS.

#### 3.1.4 Deleted.

#### 3.1.5 THE OPERATIONAL CLOCK (on A3A5 and A3A11)

#### 3.1.6 The Primary and Secondary Dividers (on A3A5)

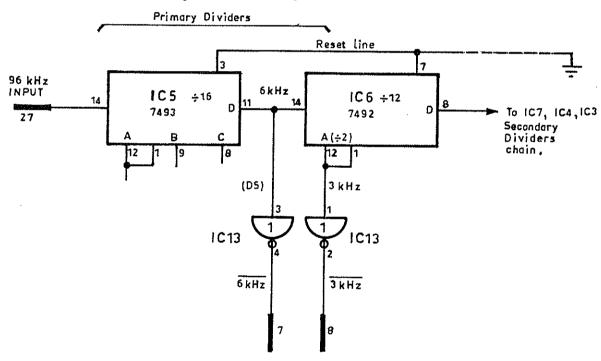

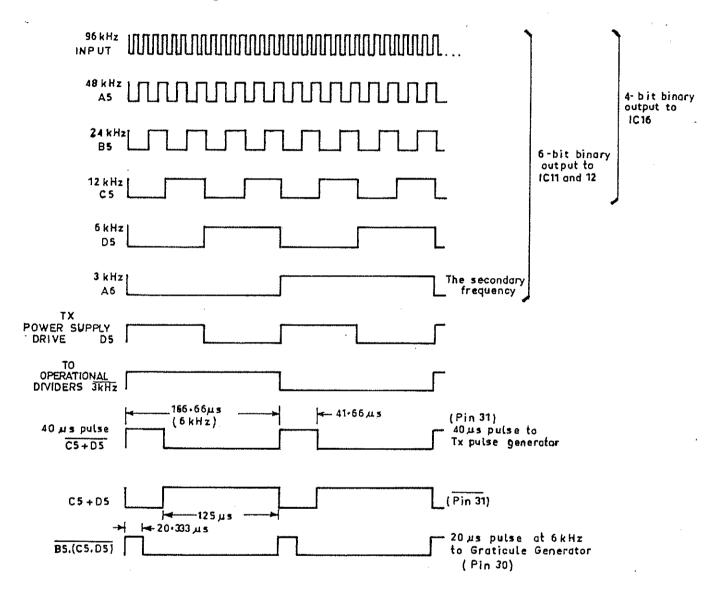

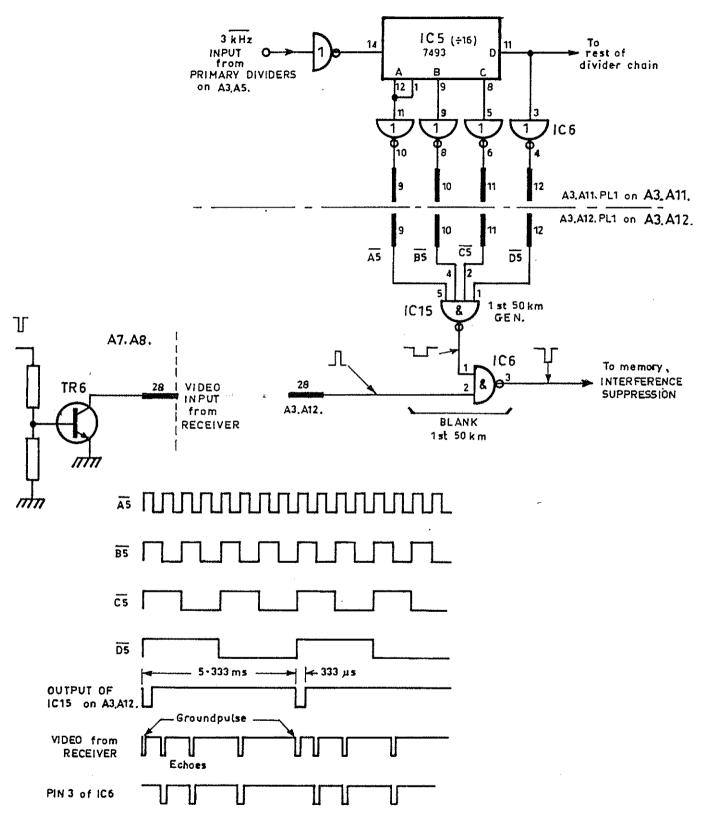

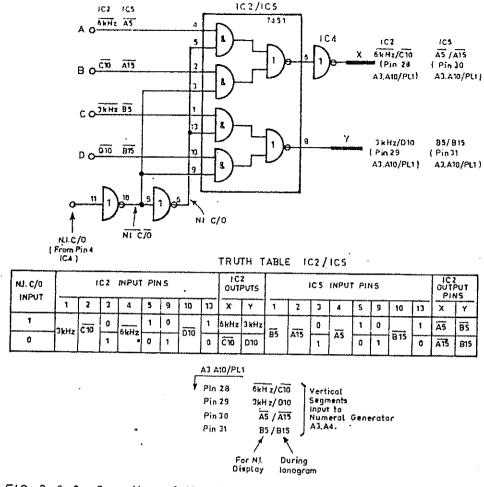

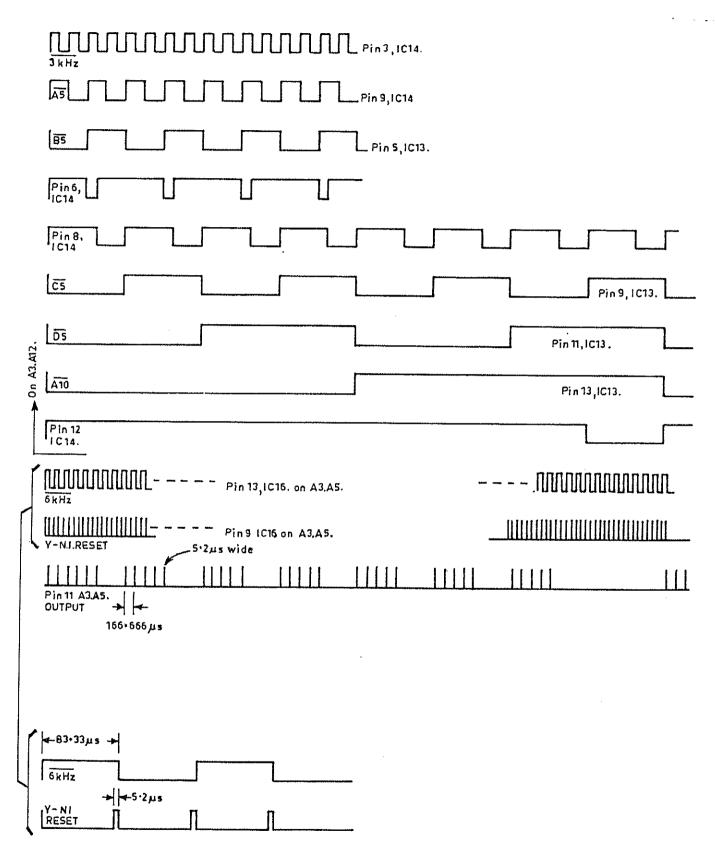

The Primary Frequency, 96kHz, is divided by 32 to produce the Secondary Frequency, 3kHz. The Secondary Dividers then follow, dividing the 3kHz down to one pulse-per-second to drive the chronometer. The output of the Primary Dividers (3kHz) also drives the Operational Dividers located on A3All.

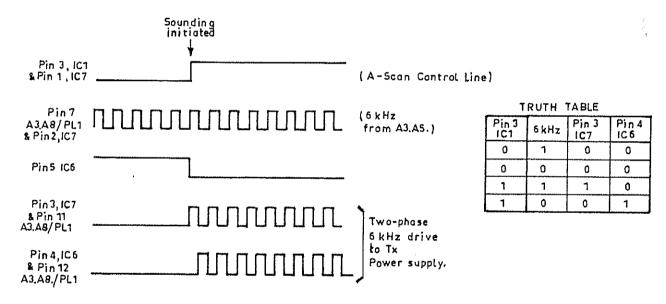

The Primary Dividers consist of IC5 and portion of IC6. The first is a 7493 divide-by-16, four-bit binary counter, the output being 6kHz. IC6 is a 7492 divide-by-12 counter, the first flip-flop is the last stage of the Primary Dividers and provides a division of two, the output (pin 12) being 3kHz.

The Secondary Dividers consist of the latter portion of IC6, dividing the 3kHz by six, followed by three 7490 decade counters IC7, IC4 and IC3. The last divider, IC3, provides a division of five. The overall division ratio of the Secondary Dividers is 3000.

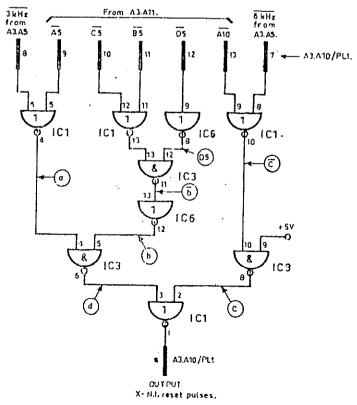

FIG. 3. 1. 2. Primary Dividers of the clock on A3.A5.

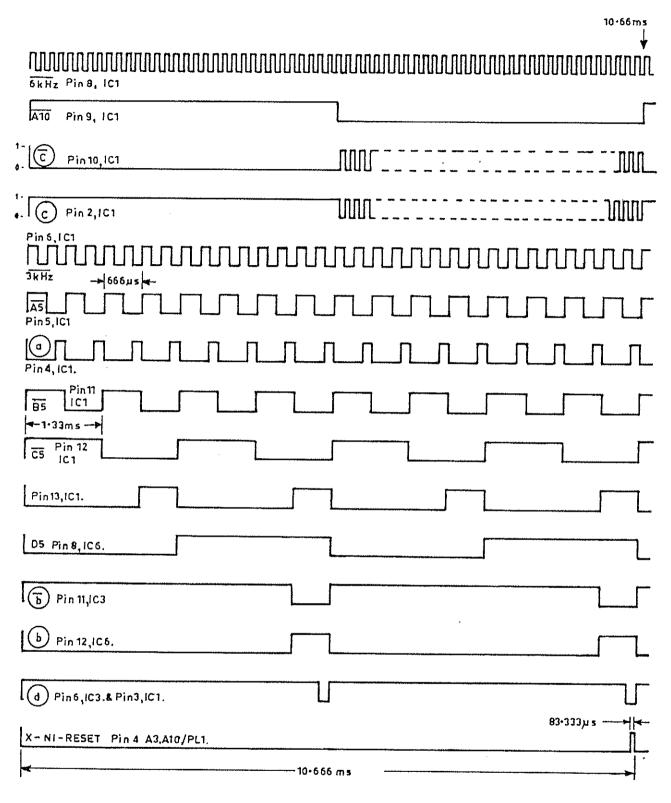

There are a number of outputs derived from the Primary Dividers for external circuit functions:

(a) A six-bit binary output for ICll and ICl2, on A3A5, which is part of the Numeral Generation Circuitry. These derive a four-bit BCD code used to generate the vertical segments of the numerals (see Section 3.6). This output is derived from the 96kHz input and the outputs of each divider in IC5 plus the secondary frequency, viz 96kHz

48kHz (A5) 24kHz (B5) 12kHz (C5) 6kHz (D5) 3kHz (A6)

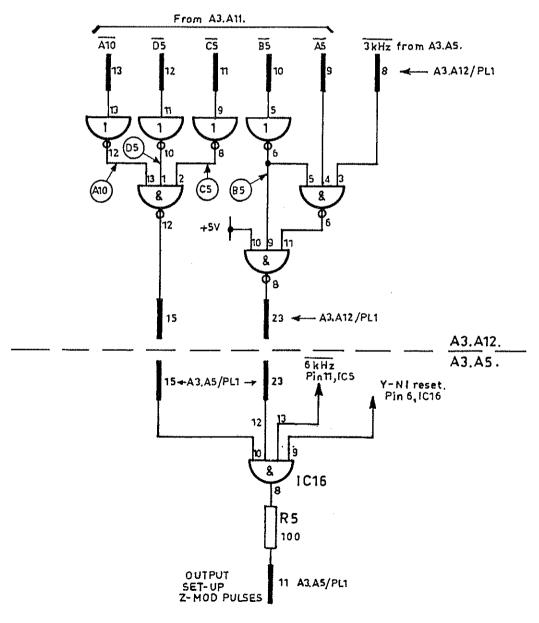

- (b) A four-bit binary output for one four-input gate of IC16 which is part of the Control System and generates the Y-NI timebase reset pulse. (See Section 3.7). This output is derived from the input and the A, B and C outputs of IC5.

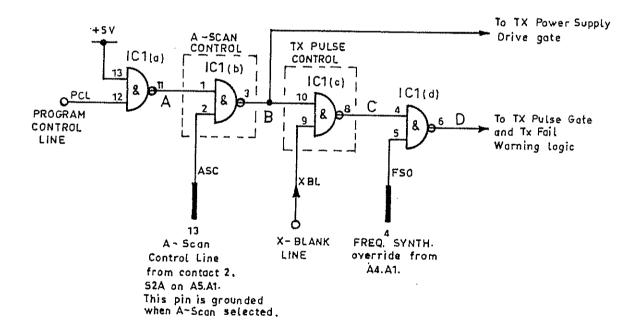

- (c) The 6kHz output of IC5 is inverted (6kHz) and this drives the Transmitter power supply via the CONTROL LOGIC (A3A8) and also provides one input for the other four-input gate of IC16 used to generate the set-up pattern unblanking pulses. (See Section 3.7).

In addition, two other outputs are derived by ancillary circuitry:

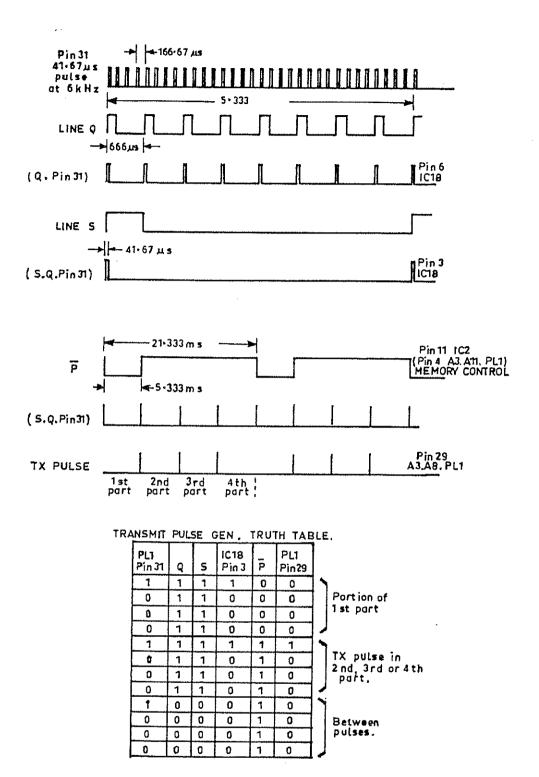

- (d) 41.66μS pulses at 6kHz for the Transmit Pulse Generator on A3All.

- (e) 20.83 $\mu$ S pulses at 6kHz for the Graticule Generators on A3All.

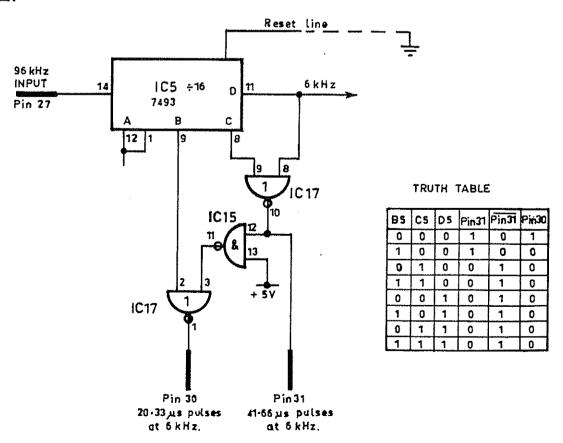

FIG. 3.1.3. Derivation of 41.66 μs pulses and 20.83 μs pulses from Primary Dividers.

A single two-input NOR gate (from IC17) combines the C and D outputs of IC5, as shown in figure 3.1.3, the resulting 41.66 $\mu$ S, 6kHz pulses appearing on pin 31 of A3A5. This output is inverted and becomes one input to another two-input NOR gate (also from IC17), the other input being the B output of IC5. This produces 20.833 $\mu$ S wide pulses at 6kHz, which output on pin 30 of A3A5.

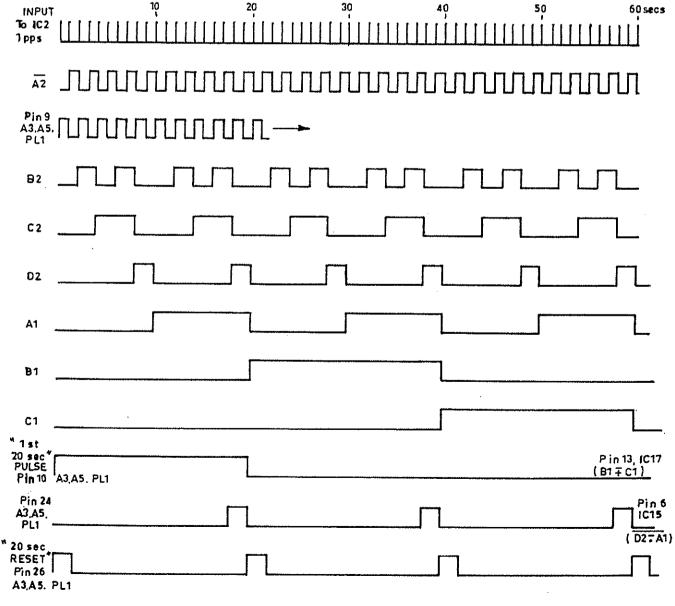

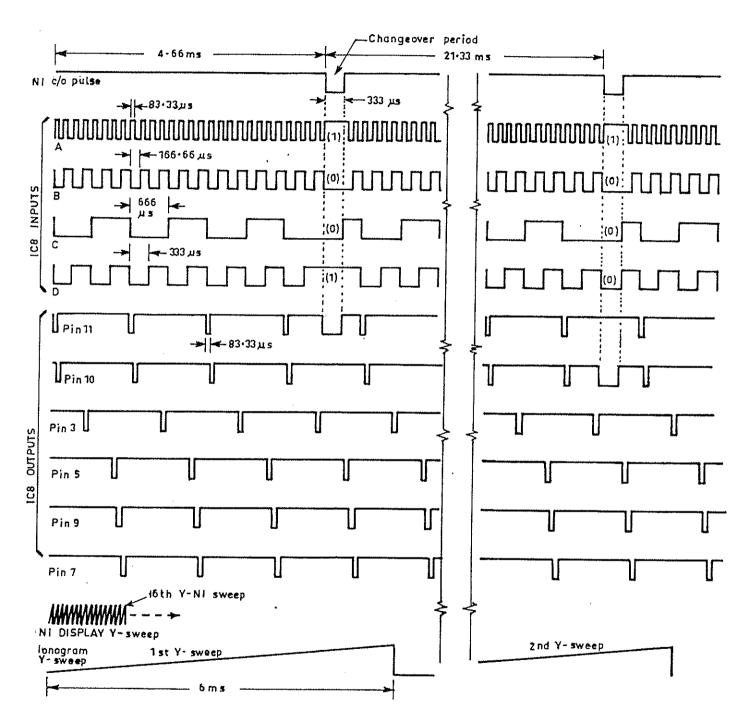

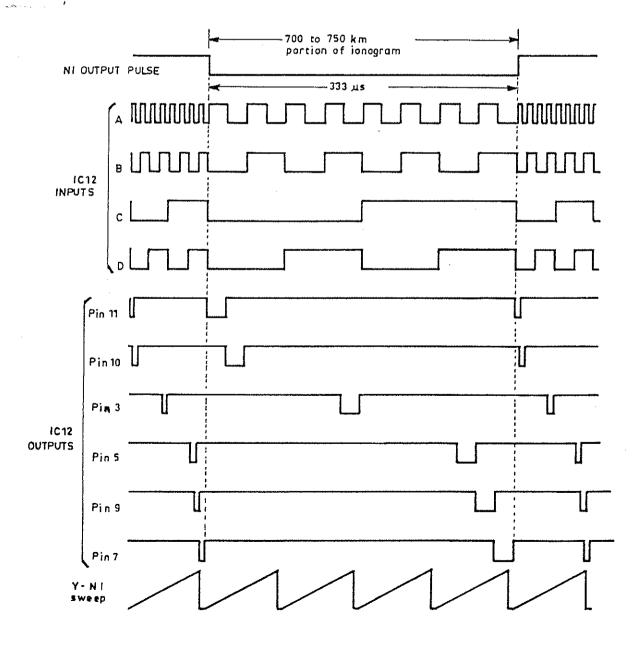

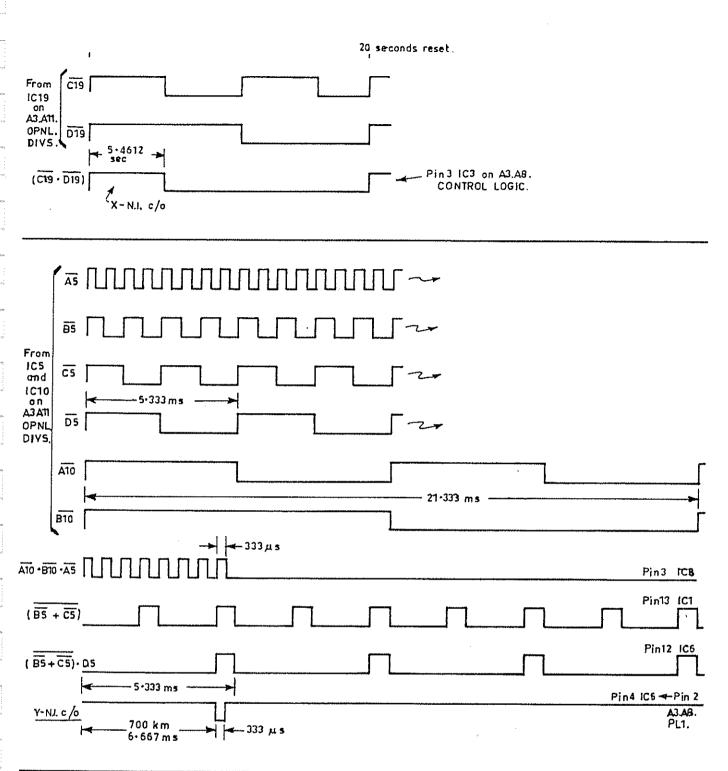

The pulse diagrams for the Primary Dividers showing all the outputs are given in figure 3.1.4.

FIG. 3.1.4. Pulse Diagrams, Primary Dividers' outputs.

## 3.1.7 The Operational Dividers (on A3A11) (Dwg: CD-225Y1, also refer dwg: CB-34Y1)

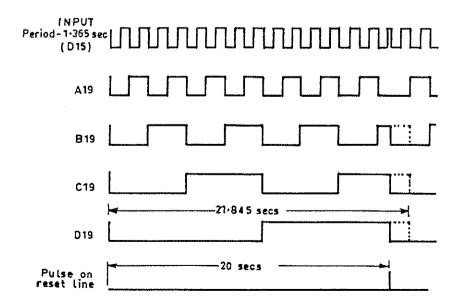

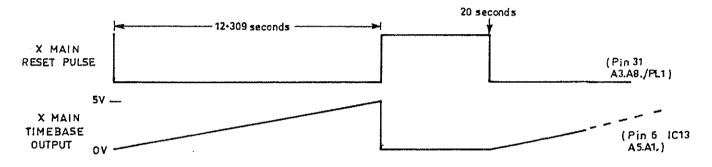

This provides sixteen outputs from four 7493 divide-by-16 four-bit binary counters connected in a chain. The A  $(\div 2)$ , B  $(\div 4)$ , C  $(\div 8)$  and D  $(\div 16)$  outputs of each IC provide outputs which are, respectively, twice the period of the previous one. The whole divider chain is reset at twenty second intervals by a pulse derived in the seconds dividers of the CHRONOMETER on A3A5.

The first divider in the chain is IC5. The input is the 3kHz output from the Primary Dividers. An inverter in series with the input to IC5 inverts this again. Each counter output line has an inverter in series with it, three hex-inverters being used; IC6, IC11 and IC16. Outputs to external circuitry and the other circuitry on A3All are taken from both inverted and direct outputs of the counters as required.

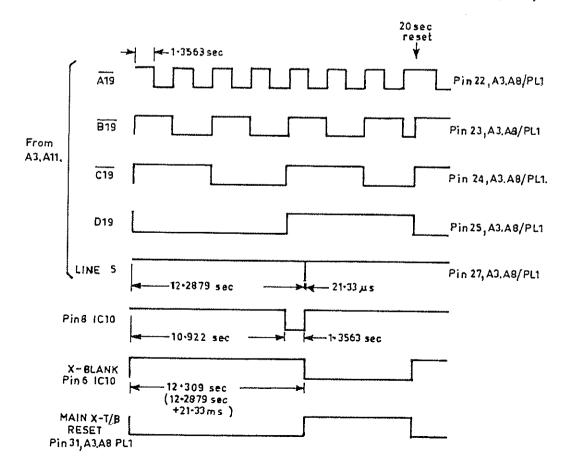

The reset pulse from the Seconds Dividers on A3A5, via pin 26 of A3All/PLl, is differentiated and then inverted to provide a narrow, positive-going reset pulse for the four counters, IC5, 10, 15 and 19. The last two counters in the chain (IC15 and IC19) are actually reset before completing their count. The D output period of IC19 would normally be 21.85 seconds but the reset truncates this at 20 seconds. The last pulse of the D output of IC15 is also shortened. This action is illustrated in figure 3.1.5.

The A, B, Cand D outputs of IC5 are designated A5, B5, C5 and D5, the outputs of the other three counters in the chain are also designated accordingly, i.e. A15, B15, etc. for IC15. The inverted outputs are designated A5, B5, etc.

The period of each output, from one negative-going edge to the next (encompassing a 0 and a 1) is listed in the following table. The width of each 0 or 1 pulse within that period is equal to half the output period.

| Out | put Period | Output Period |

|-----|------------|---------------|

| A5  | 666µS      | Al5 170.666mS |

| B5  | 1.333mS    | Bl5 341.333mS |

| C5  | 2.666mS    | Cl5 682.666mS |

| D5  | 5.333mS    | Dl5 1.3653S   |

| A10 | 10.666mS   | A19 2.7306S   |

| B10 | 21.333mS   | B19 5.4613S   |

| C10 | 42.666mS   | C19 10.9226S  |

| D10 | 85.333mS   | D19 21.8453S  |

The input period is 333µS (3kHz)

FIG. 3.1.5. Illustrating the action of the 20 second reset pulse on the final binary counters in the Operational Dividers.

The sixteen inverted outputs are on pins 9 to 25 inclusive of A3All/PL1.

Four groups of the inverted outputs drive external circuitry. These are as follows:

#### 1. Pins 9 to 23, A5 to B19 inclusive

These outputs are used by part of the Numeral Generation Circuitry for commutation of the Chronometer outputs and derive a four-bit BCD code used to generate the horizontal segments of the numerals. (See Section 3.6.)

#### 2. Pins 9 to 13, $\overline{A5}$ to $\overline{A10}$ inclusive

These outputs drive circuitry, located on A3A12, which is part of the Control System and Signal Processing System (see Sections 3.7 and 3.5).

#### 3. Pins 15 to 25, $\overline{\text{ClO}}$ to $\overline{\text{Dl9}}$ inclusive

Provides a naturally advancing 10-bit binary number for frequency scan operation of the Frequency Synthesizer.

#### 4. Pins 22 to 25, Al9 to Dl9 inclusive

These outputs go to the Control Logic, A3A8, for circuitry which derives the X-blank pulse for the Ionogram display and portion of the NI-changeover pulse (see Section 3.7).

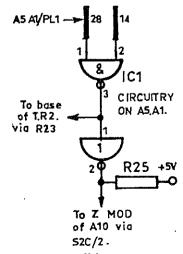

In addition, pin 14 (BlO) goes to A5Al to offset the CRT deflection during the NI display (see Section 3.8).

#### 3.1.8 Additional outputs and circuitry

The Operational Clock provides a further five outputs, these being derived from the other circuitry on A3All. The circuitry and outputs are as follows:

- 1. The Graticule Generator provides pulses to brighten the CRT trace at the appropriate times to 'write' the graticule on the Ionogram. These pulses are derived by gating various outputs from the Operational Dividers. An output from the Graticule Generator also provides pulses for the X-Blank Generator in the CONTROL LOGIC (A3A8).

- 2. The Transmit Pulse Generator provides 40μS, TTL level pulses for the TRANSMITTER. It also provides an output that controls the operation of the SIGNAL PROCESSING CIRCUITRY.

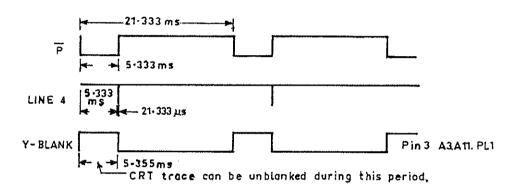

- 3. The Y-Blank Generator provides a pulse to the CONTROL LOGIC that allows the CRT trace to be unblanked (brightened) only during the first 5.333mS of the 6mS Y-sweep of the Ionogram holding the trace blanked between sweeps (see Section 3.8).

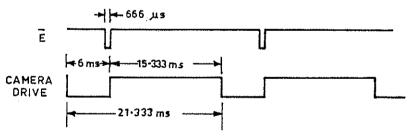

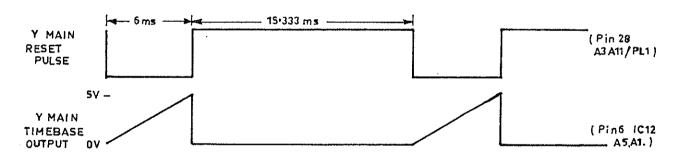

4. The Camera Drive Generator. The camera motor is a DC motor that normally runs at a speed which is too fast for this application. Its speed is reduced by pulsing the motor drive voltage. This circuit provides a 15.33mS pulse at the end of each 21.33mS period which allows the camera motor to operate at the required speed.

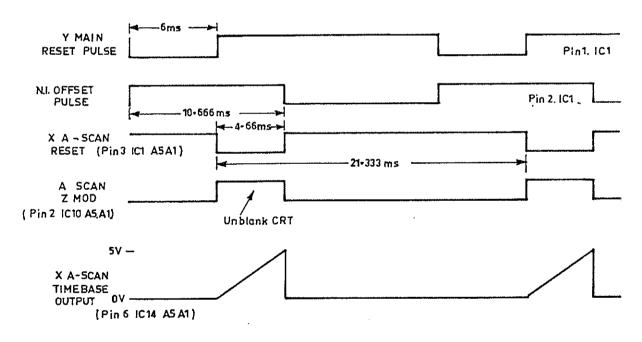

In addition to this function, the same waveform is used as the Y MAIN timebase reset and to generate the X A-SCAN reset in conjunction with the BlO output from the Operational Dividers (see Section 3.8).

#### 3.1.9 The Graticule Generator

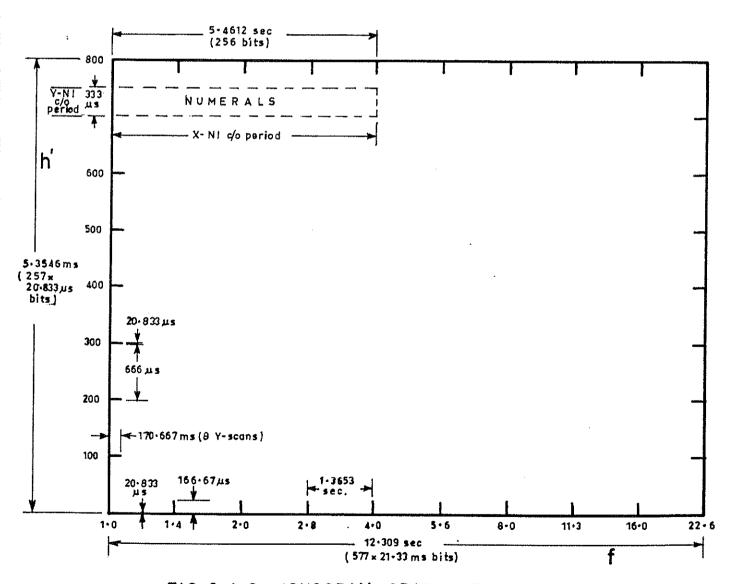

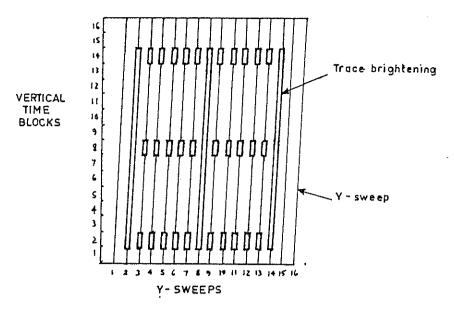

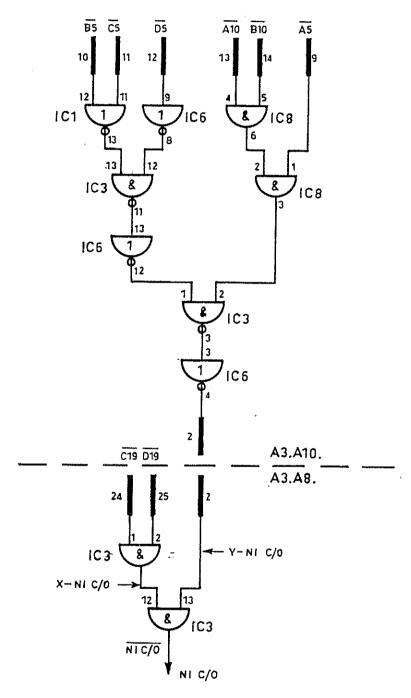

The graticule and the time relationships are illustrated in figure 3.1.6.

FIG. 3. 1. 6. IONOGRAM GRATICULE.

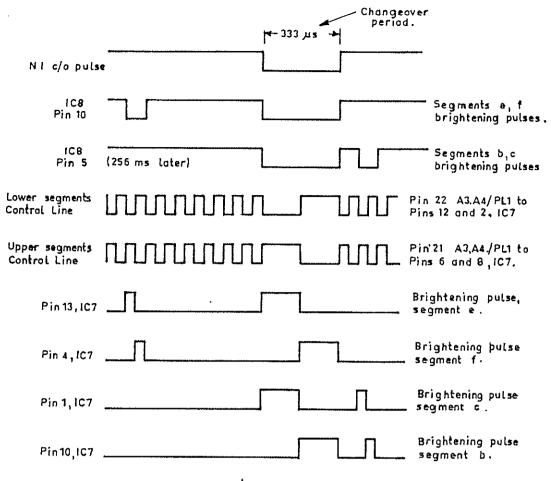

On drawing CD-225Y1, a series of NAND-gates and AND-gates grouped together in two columns is designated the GRATICULE GENERATOR. To the left of these is a series of AND-gates which gate together outputs of the Operational Dividers to drive twelve inputs to the Graticule Generator gates. IC's 3, 4, 9, 8, 14 and 17 provide gates for this part of the circuit. The Graticule generator input lines are marked 0 to Z. An additional input enters via pin 30 and comes from the Primary Dividers on A3A5. This input is designated N, making a total of 13 inputs to the Graticule Generator.

The left hand row of gates in the Graticule Generator, on dwg CD-225Yl, are two-input AND-gates involving IC's 3, 8, 9, 12, 14 and 18, which produce inputs for the eight, two-input NAND-gates on the right (involving IC7 and ICl3) to produce the graticule brightening pulses in parallel form.

The AND-gates drive eleven inputs to the NAND-gates of IC7 and IC13, some gate inputs being paralleled. These eleven inputs are designated A, B, C, D, E, F, G, H, J, K, L. The outputs of IC7 and IC13 are designated 1 to 8 on drawing CD--225Y1. Each of these lines carry pulses which write the parts of the graticule as follows:

<u>Line 1</u> Frequency markers, bottom line (zero range)

Line 2 Frequency markers, top line (max. range)

Line 3 Bottom border line

Line 4 Top border line

Line 5 Right hand border line

Line 6 Left hand border line

Line 7 Height markers, left hand

Line 8 Height markers, right hand

The individual circuits that derive the waveforms for the Graticule Generator inputs 0 to Z, and each input waveform appear in drawings GC-28Y1, GC-28Y2 and GC-28Y3.

The waveform on input N and the NAND-gate inputs A to L are illustrated in drawing GC-29Yl. The waveforms on the output lines 1 to 8 are also included.  $\dot{}$

The left hand border line of the graticule is blanked between 700 km and 750 km so that the first numeral in the ident and date/time numeral display on the ionogram is not obscured. The NI-changeover pulse (from pin 6, A3All/PLl) and the graticule pulses are gated together in a two-input NAND-gate (one gate of IC2) to achieve this.

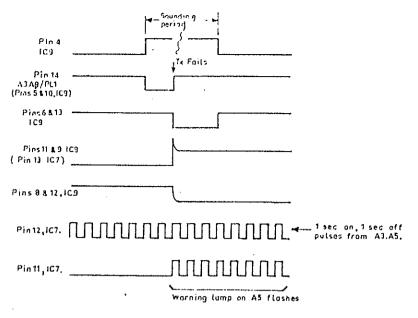

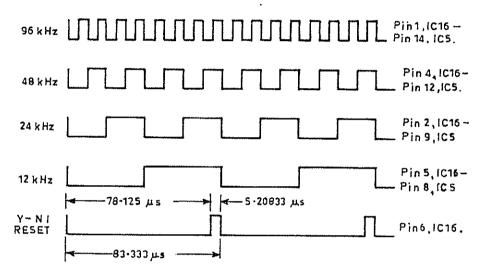

#### 3.1.10 The Transmit Pulse Generator

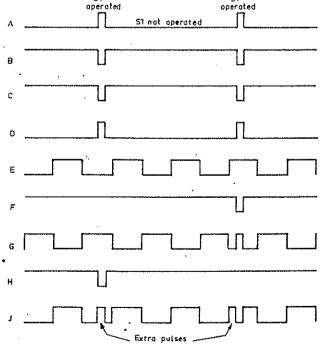

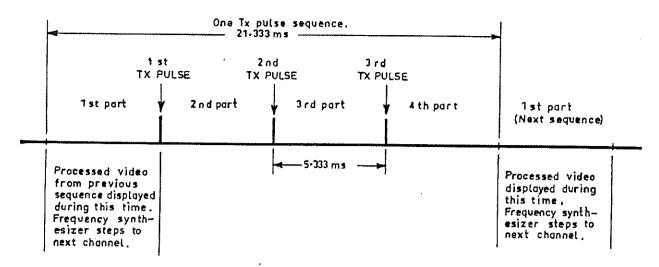

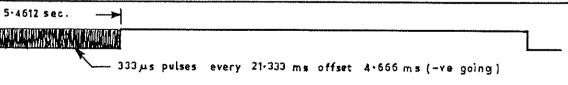

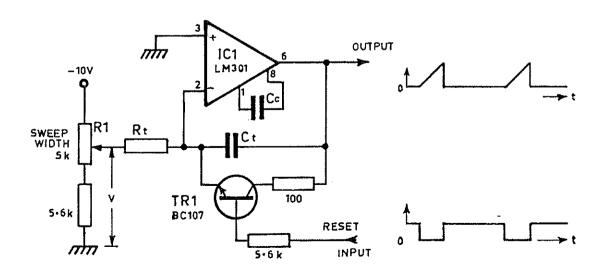

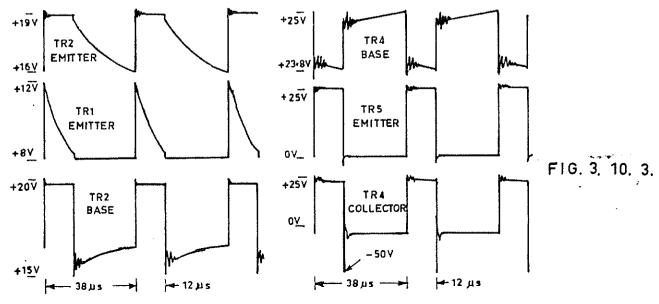

This portion of the circuitry on A3All involves three AND-gates from ICl8 and one NAND-gate from IC2 which functions as an inverter, inverting the waveform on input line P, which becomes P. The 41.66 $\mu$ S pulses generated from the Primary Dividers on A3A5 enter on pin 3l of A3All/PLL. Three other inputs, Q, S and P, come from the Graticule Generator inputs. The result is a group of three 41.66 $\mu$ S pulses at 5.33mS intervals followed by a gap of 10.66mS. There is no transmit pulse in the 'lst part' of the transmit pulse sequence. The waveforms are illustrated in figure 3.1.7. The transmit pulses output on pin 29 of A3All/PLL.

The inverted wave form of input P (P) becomes the 'lst part Control Pulse' for the SIGNAL PROCESSOR on A3ALL.

FIG. 3, 1, 7. Derivation of Transmit Pulse.

#### 3.1.11 The Y-Blank Generator

This is one NAND-gate from IC2. One input is output line 4 of the Graticule Generator, the other input being P. The output goes via pin 3 of A3All/PLL, to the CONTROL LOGIC (A3A8) portion of the Control System (see Section 3.7). The waveforms are illustrated in figure 3.1.8.

#### 3.1.12 The Camera Drive Generator

This is one AND-gate from ICE. One input is the inverted waveform from input line  $E(\overline{E})$  using one NAND-gate from IC2 connected as an inverter. The other input is  $\overline{P}$ . The output goes via pin 28 of A3All/PL1 to the Camera motor via the PROGRAM unit, A5Al. The waveforms are illustrated in figure 3.1.9. The Y-MAIN and the X A-SCAN timebases are located on A5Al and conveniently use this waveform to reset the sweeps (see Section 3.8).

FIG. 3.1, 8. Derivation of Y-BLANK

FIG. 3.1.9. Derivation of Camera Drive.

#### 3.1.13 THE CHRONOMETER

(Dwgs: CB-34Y1, CD-224Y1, CD-221Y1, CD-22OY1, CD-218Y1)

The Chronometer circuitry is spread across five of the plug-in printed circuit cards, these being A3A5, A3A7, A3A3, A3A2 and A3A1 (refer CB-34Y1).

The divider chain is driven by the lpps output of the Secondary Dividers on A3A5.

Each of the Chronometer Dividers produces a group of four-bit BCD numerals representing the date, time, etc., numbers. The numerals of each number are multiplexed in sequence onto four output lines common to each of the Divider assemblies A3A5, A3A7, A3A3, A3A2 and A3A1. These four common lines go to the 'Numeral Input' of the NUMERAL GENERATOR A3A4. The numerals

are then written on the CRT in the required sequence. The 'tens' numeral of each number is written first, followed by the units, except for the Days Divider output where the 'hundreds' numeral precedes them as it is a three figure number.

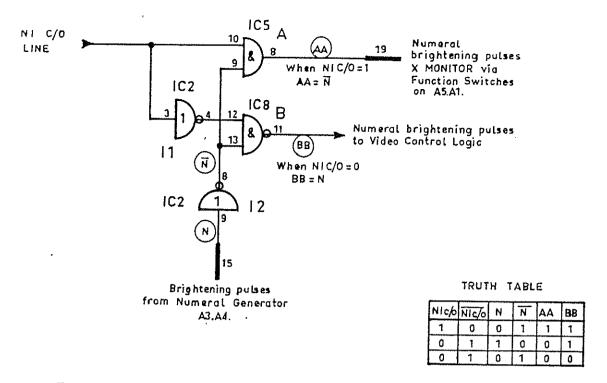

The Variable Number and Station Number are also multiplexed on to the four common output lines. These appear on the ionogram preceding the date/time numbers. For the 'Numeral Indication ' (NI Display) the Station Number is replaced by the Seconds from the Chronometer. This action, and the multiplexing of the numerals is accomplished by the COMMUTATION GENERATOR located on A3A6 and A3A10. (See Section 3.6)

### 3.1.14 The Seconds Dividers (Dwg: CD-227Y1)

This is the first stage of the Chronometer Dividers and comprises ICl and IC2 on A3A5. IC2 is a type 7490 decade counter. The lpps output from IC3 drives the input of IC2 which produces a 0.lpps output to ICl, a 7492 divide-by-l2 counter. Only the ÷6 portion of ICl is used, producing a one-pulse-per-minute output (lppm). The A, B, C and D outputs of IC2 present a four-bit BCD code representing the 'units' of seconds. This is multiplexed onto the four common output lines, pins 2, 3, 4, 5 of A3A5/PLl, via quad NAND-gates IC9 and IClO. Only the A, B and C outputs of ICl are required to represent the 'tens' of seconds. This output is multiplexed onto the four common output lines via the quad NAND-gates IC8 and IClO. See Section 3.1.16 for the operation of the output multiplexing circuitry.

To set the Seconds Dividers to a given time the dividers IC3, IC2 and IC1 are all set to zero by operating Sl. This causes the 'reset l' terminal of each divider to go HI resetting each divider to zero. If Sl is held operated, the outputs of each divider remain at zero allowing the Chronometer to be synchronised to a time standard (e.g. VNG, WWV, etc.).

#### 3.1.15 Seconds Dividers Auxiliary Outputs

There are four auxiliary outputs from the Seconds Dividers.

- (a) The A output of IC2 is inverted by one gate in IC15, acting as a buffer, and provides one pulse every other second (i.e. one second on, one second off) at pin 9 of A3A5/PLL. This is used to pulse the 'TX FAIL' warning light on the front panel of the PROGRAM unit A5A1, the pulses going via circuitry in the CONTROL LOGIC, A3A8.

- (b) The B and C outputs of ICl go to the two inputs of one NOR-gate in ICl7. The output (pin 13, ICl7) goes HI for the first 20 seconds of each minute. This output goes to the program decoding circuitry of the Minutes Dividers (refer dwgs: CB-34Yl and CD-224Yl). This is designated the 'lst 20 SECONDS' pulse.

- (c) The D output of IC2 and the A output of IC1 go to the two inputs of one gate in IC15 (pins 1 and 2). The output (pin 3, IC15) is inverted by a further gate and goes to pin 24 of A3A5/PL1. This output goes HI from the 18th to the 20th second of each twenty seconds. This pulse is required to control the camera motor drive and shutter at the end of each programmed sounding. It goes to the Program unit, A5A1.

- (d) The B, C and D outputs of IC2 and the A output of IC1 go to four inverters made up from gates in IC14. This IC is a type 7401 quad NAND-gate with open-collector outputs. The resultant is a two second long pulse at the commencement of each twenty seconds. It resets the OPERATIONAL DIVIDERS on A3A11, passing via pin 26 of A3A5/PL1.

Each twenty seconds is called the "sounding period" as it is possible for the ionosonde to execute a sounding during these periods. However, if a sounding is initiated, the Transmitter will not be pulsed and the display will not commence until the end of the first two seconds in a twenty second sounding period.

FIG. 3.1, 10. Pulse Diagrams Seconds Dividers.

#### 3.1.16 Chronometer Dividers Output Multiplexing

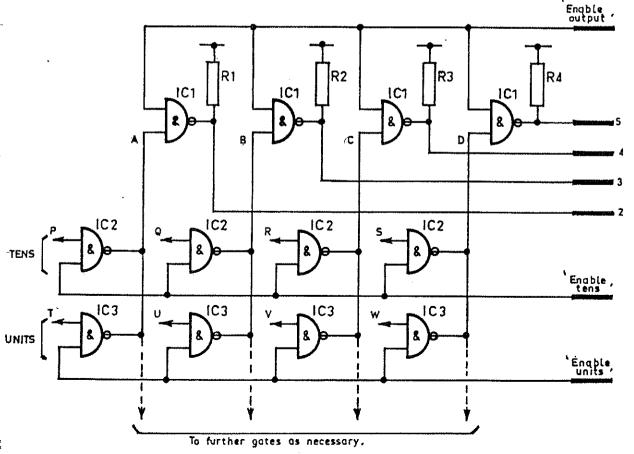

Each stage of the Chronometer has a four-bit BCD output indicating the date, time, etc. (in parallel form) as mentioned previously. These outputs are multiplexed in sequence onto four lines which go to the Numeral Generator input. The circuitry to accomplish this is essentially the same for each stage of the Chronometer. The general form is shown in figure 3.1.11.

A number of quad two-input NAND-gates having open-collector outputs are used. The gates of ICl drive the four output pins 2, 3, 4, 5. Four inputs of ICl, designated A, B, C, D, are driven by the outputs of IC2 and IC3. The other inputs are commoned and go to the 'enable output' pin which is driven by the Commutation Generator A3A6.

The four-bit BCD output of the TENS divider of the particular stage of the Chronometer goes to the inputs P, Q, R, S of IC2. The other inputs are commoned and go to the 'enable tens' pin which is driven by the Commutation Generator. Similarly, the BCD output of the UNITS divider of the particular Chronometer stage goes to inputs T, U, V, W of IC3, the other four inputs being driven by the Commutation Generator via the 'enable units' pin. -

When a number from the particular stage of the Chronometer is not required, the 'enable output' pin is held LO by the Commutation Generator causing the outputs of each gate in ICl to go HI, "pulled up" by the resistors Rl, R2, R3, R4. With a HI (or 1) on each output line, the Numeral Generator produces a blank, or no output, and nothing is displayed on the CRT for the period that the pins 2, 3, 4, 5 remain HI.

The Commutation Generator selects each number to be displayed by driving the 'enable output' pin HI on each Chronometer stage in sequence. Each gate in ICl will act as an inverter for the levels on each of the inputs A, B, C, D. The highest value numeral is displayed first so the Commutation Generator next drives the 'enable tens' pin HI. The BCD data on the inputs

FIG. 3. 1. 11. Chronometer Dividers Output Multiplexing circuitry.

P, Q, R, S of IC2 is then inverted at the outputs of each gate in IC2 which drives the A, B, C, D inputs of IC1 which inverts this again. Thus, the four-bit BCD numeral from the particular Chronometer divider output appears on the output pins 2, 3, 4, 5. The Numeral Generator then causes the particular numeral to be displayed.

Following the display of the tens numeral, the Commutation Generator then drives the 'enable units' pin HI and the 'enable tens' pin IO. The units BCD numeral on T, U, V, W is then passed to the output pins 2, 3, 4, 5 in a similar fashion to the tens numeral.

When the number for the particular Chronometer divider stage has been displayed, the Commutation Generator then drives the 'enable output' pin IO and selects the next stage in the sequence.

Other numerals, and blanks, are added by adding further gates to drive the A, B, C, D inputs of ICl as indicated in figure 3.1.11.

The overall arrangement and selection of the Chronometer outputs for the numeral display are presented schematically in drawing CB-30Y1.

### 3.1.17 The Minutes Dividers (A3A7) (Dwg: CD-224Y1)

The one-pulse-per-minute (lppm) output of the Seconds Dividers enters the Minutes Units divider IC9, via a circuit which adds an extra pulse to advance the count when the switch Sl is operated. This 'advance count' circuit is used in each subsequent stage of the chronometer dividers to enable the Chronometer to be set to the required time. The operation of this circuit is explained in paragraph 3.1.18 following.

IC9 and IC8 are type 7490 decade counters. Each is reset to zero at the end of sixty minutes. One gate in IC7 nands the B and C outputs of IC8 producing a positive-going pulse which is inverted to reset IC8 and IC9. This action is illustrated in figure 3.1.12. The B and C outputs would normally be as shown by the dotted lines. The reset action reverses their condition with a delay of several nanoseconds producing a very narrow pulse at the end of minute 60, resulting in an output of one-pulse-per-hour from the C output of IC8.

FIG. 3.1.12. Chronometer Minutes Divider reset action.

#### 3.1.18 The 'Advance Count' circuit

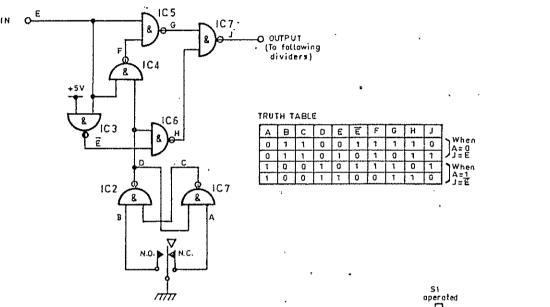

The 'advance count' circuit is illustrated in figure 3.1.13. Seven NAND-gates are used, ICl and IC2 forming a 'SET-RESET', or S-R flip-flop to 'debounce' the pulse from the contacts of S1.

When Sl is not operated, the output of the S-R flip-flop, D, is 10 and the incoming pulses are transferred to the output, J, via IC5 and IC7.

If Sl is then operated momentarily while the input (E) is IO, J will go HI momentarily, adding an extra pulse to the incoming pulse train. As a divider is driven via this circuit, it will advance its count by one on the negative-going edge of the extra pulse, i.e. when Sl is released. If Sl is held operated the incoming pulses will be merely inverted at the output, J.

FIG. 3. 1. 13, The 'Advance Count' circuit.

FIG. 3, 1, 14. Pulse diagrams for Advance Count circuit.

If Sl is operated momentarily while E is HI, J will go LO momentarily, the following divider advancing its count by one the moment Sl is operated.

The action of Sl is illustrated in the pulse diagram of figure 3.1.14. The truth table for the advance count circuit is in figure 3.1.13.

#### 3.1.19 Program Decoding Circuitry

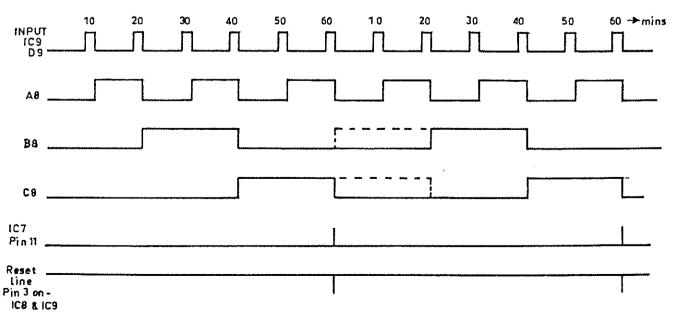

Pulses used to program the operation of the ionosonde are derived by circuitry on A3A7 involving IC5, IC10, IC11, IC12, IC13 and IC14. This circuitry produces 20-second long output pulses at intervals of 1 minute, 5 minutes and 15 minutes to three pins on A3A7/PI1.

IC11 and IC12 are type 7442 four-bit BCD-to-decimal decoders. The BCD output of the first decade divider (IC9) is decoded by IC12. The 'O' output of IC12 (pin 1) goes IO for the zero minute or commencement of the count. The '5' output (pin 6) goes IO for the fifth minute. Similarly IC11 decodes the BCD output of IC8, the MINUTES TENS divider. The 'O' output goes LO from zero to ten minutes, the '1' output goes IO from ten to twenty minutes, the '3' output goes IO from thirty to forty minutes and the '4' output goes IO from forty to fifty minutes.

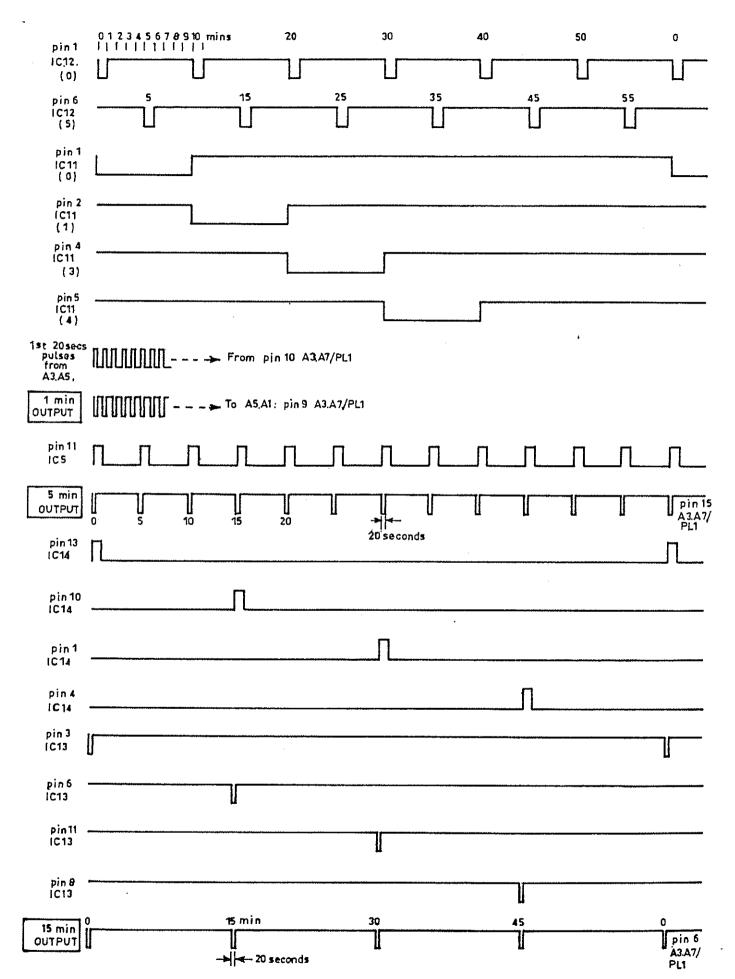

The 5 MIN output is produced by nanding the 0 and 5 outputs of ICl2 in one gate from IC5. This produces pulses of one minute duration every five minutes, i.e. at minutes 0, 5, 10, 15, 20, 25 etc. This output (pin 11, IC5) is then nanded in another gate from IC5 with the 'lst 20 SECS' pulses producing pulses of twenty seconds duration at minutes 0, 5, 10, 15 etc. on pin 15 of A3A7/PLL. This operation is illustrated in figure 3.1.15.

The 1 MIN output (pin 9, A3A7/PL1) is produced by inverting the 1st 20 SECS pulses.

The 15 MIN output is produced by nor-ing appropriate outputs from ICll and ICl2 to produce pulses of one minute duration at 0, 15, 30 and 45 minutes on four separate lines from pins 13, 10, 1 and 4 respectively, of ICl4. Each of these is then strobed by the 1st 20 SECS pulses in four gates (ICl3), reducing the duration of each of the pulses to twenty seconds. A four-input NAND-gate, ICl0, combines them then in serial form, the output appearing on pin 6 of A3A7/PILL. Refer also the figure 3.1.15 for the pulse diagrams.

In addition, two further outputs are provided for the PRESET PROGRAM unit A3A9 which is an optional unit not normally included in the equipment. Two gates from ICl5 derive inputs from appropriate output lines of ICl4. The outputs of these two gates are subsequently inverted producing pulses of one minute duration at minutes 15 and 45 (pin 2, A3A7/PL7), and minute 30 (pin 3, A3A7/PL1).

### 3.1.20 <u>The Hours Dividers (A3A3)</u> (Dwg: CD-221Y1)

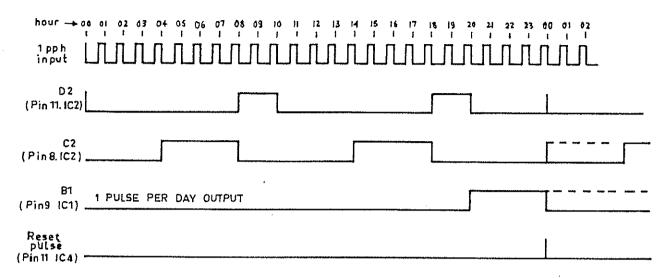

Two type 7490 decade counters are used in this circuit. Both counters are reset to zero at the end of each 24 hours. The lppm from the Minutes Dividers enters IC2 via an 'advance count' circuit. The hours units advance by one when Sl is operated. The output of IC2 drives ICl via another advance count circuit which enables the hours tens to be advanced by operating S2. The C output of IC2 and the B output of IC1 are nanded together and the resulting pulse inverted to produce a negative-going reset pulse at the end of the 24th input pulse. This operation is illustrated in the pulse diagrams of figure 3.1.16 and is similar to the reset action for the Minutes Dividers.

The BCD output code multiplexing differs from that for the other dividers in that the Minutes numerals code is multiplexed onto the output lines (pins 2, 3, 4, 5 of A3Al/PLl) immediately following the Hours numerals via common circuitry spread across the two assemblies A3A7 and A3A3. Commutation for the Minutes output multiplexing is derived via IClO on the Hours Dividers.

FIG. 3, 1, 15, Derivation of Program Pulses.

In addition, a six-bit BCD output from ICl and IC2 is provided for the PRESET PROGRAM unit A3A9 (optional) via ICll, a hex-buffer/driver).

The l-pulse-per-day output is taken from the B output of ICl and goes to the Days Dividers via pin 25 of A3A3/PLL.

FIG. 3. 1. 16. Hours Dividers reset action.

# 3.1.21 <u>The Days Dividers (A3A2)</u> (Dwg: CD-220Yl)

This consists of three type 7490 decade counters in a chain, IC3, 4 and 5. The input to each counter is preceded by an advance count circuit so that the units, tens and hundreds digits may be set.

This unit provides a three digit number for each day of the year commencing at OOl for January the 1st and ending on 365 for December the 31st, except for leap years which have 366 days.

The divider chain is reset to 000 at the commencement of the 366th input count each year, or the 367th each leap year. The reset pulse is generated by IC6, an eight-input NAND-gate (7430). When all inputs are HI, the output (pin 8, IC6) goes IO, this is then inverted by IC7 providing a positive-going pulse to reset the dividers IC3, 4 and 5. As the divider chain resets within a few nanoseconds of the output of IC6 going IO, the reset pulse is very narrow.

The pulse from the output of IC6 also passes through a series of ten inverters, delaying the pulse about 100nS. This delayed pulse then appears as an extra pulse, following the 366th input pulse, at the input of the first divider IC3, via a NAND-gate (from IC16). Thus, the count advances from 000 to 001 about 100nS following resetting of the divider chain.

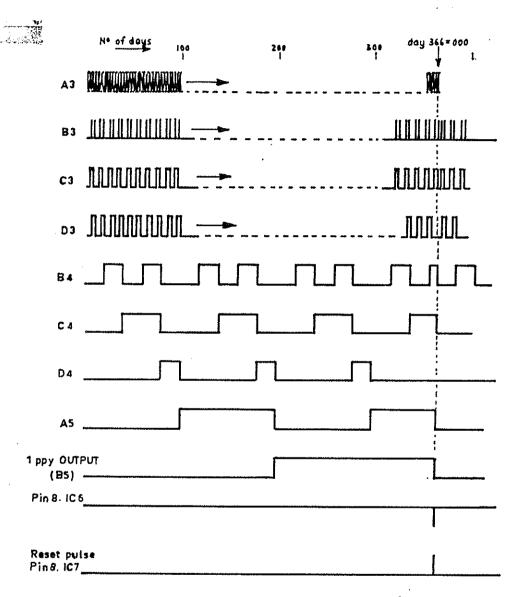

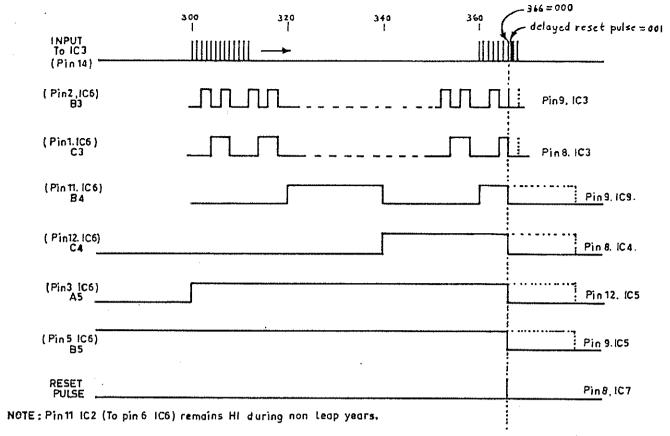

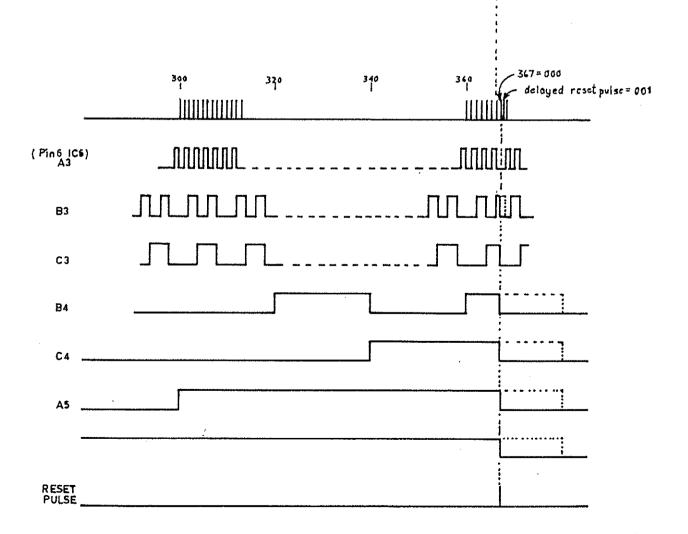

The overall operation is illustrated in the pulse diagrams of figure 3.1.17. The reset action for non-leap years is illustrated in figure 3.1.18. During non-leap years, the 'leap year reset input' (pin 28, A3A2/PL1) is held IO from circuitry located on A3A1. This causes pin 11 of IC2 to remain HI during non-leap years, allowing the reset pulse to occur at the beginning of the 366th input pulse as illustrated in figure 3.1.18. During a leap year, the 'leap year reset input' goes HI and the A output pulses from IC3 will appear on pin 6 of IC6. Consequently, all the inputs to IC6 will then only go HI at the beginning of the 367th input pulse allowing for the extra day in a leap year. This is illustrated in figure 3.1.19.

The B output of IC5 provides the 'one pulse per year' (lppy) output, going high on day 200 and remaining high until the dividers are reset. This output goes to the Years Divider A3Al via pin 26 of A3A2/PLL.

The BCD output of each divider is multiplexed through to the common output lines as discussed in section 3.1.16 via IC10, 11, 12 and 13. IC13 provides a blank before the first digit of the days number displayed.

FIG. 3.1. 17. Days Dividers pulse diagrams.

# 3.1.22 The Years Divider (A3A1) (Dwg: CD-218Y1)

A single 7490 decade counter, IC8, comprises the Years Divider. The lppy output of A3A2 enters the input of IC8 via an advance count circuit enabling the 'Years Units' digit to be set. The BCD output of IC8 only provides the units digit of the years number displayed. The BCD code for the tens digit is hard wired on the inputs of IC3 (in the output multiplexing circuitry) to produce a 7 in the numeral display for the 70's decade. This board is replaced at the end of each decade, (i.e. replacement due in 1980).

FIG. 3. 1. 18. Days Dividers reset action in non-leap years.

FIG. 3. 1. 19. Days Dividers reset action during leap years.

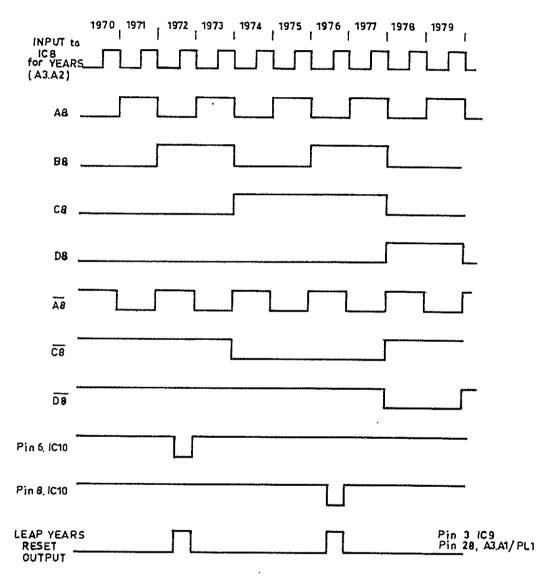

Two four-input NAND-gates (IClO) generate the 'Leap-Years-Reset' output. The A, B, C and D outputs from IC8 are nanded so that pin 6 of IClO goes IO during 1972. The A, B, C and D outputs from IC' are nanded so that pin 8 of IClO goes IO during 1976. The outputs from pin 6 and pin 8 of IClO are nanded in one gate from IC9, the output of which (pin 3) goes HI in 1972 and 1976 as required. The 'Leap-Years-Reset' output appears on pin 28 of A3Al/PLl and goes to the Days Dividers A3A2. The generation of this output is illustrated in figure 3.1.20.

FIG. 3. 1. 20. Derivation of the Leap Years Reset output.

### 3.2 FREQUENCY SYNTHESIZER

| Par. No. | <u>Title</u>                   | Draw | ring l | <u>Vo.</u>   |

|----------|--------------------------------|------|--------|--------------|

| 3.2.1    | Introduction                   |      |        |              |

| 3.2.2    | Brief Description              | CB2  | 9Yl    |              |

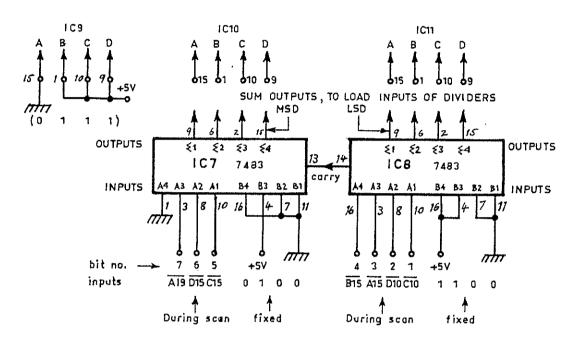

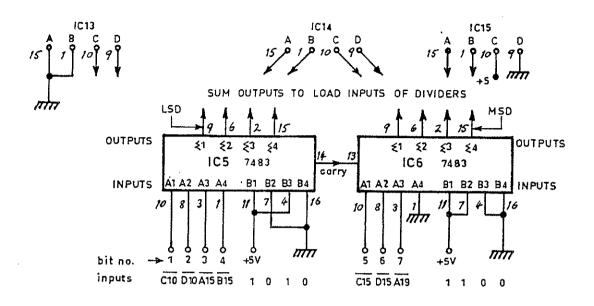

| 3.2.3    | THE DIGITAL SECTION            | CD-2 | 32Yl   | (A4Al)       |

| 3.2.4    | The Octave Divider             | 11   | 17     | II           |

| 3.2.5    | Programmable Divider A         | tt   | 11     | 11           |

| 3.2.6    | Programmable Divider B         | **   | 71     | tt           |

| 3.2.7    | The Digital Comparator         | 11   | 11     | 11           |

| 3.2.8    | THE RF SECTION .               | CD-2 | 32X2   | (A4A2)       |

| 3.2.9    | The VFO and Steering Circuitry | 17   | tt     | 11           |

| 3.2.10   | 70 MHz Oscillator and Mixer    | tt   | 11     | 11           |

| 3.2.11   | The Digital Interface Circuit  | 11   | tt     | TT .         |

| 3.2.12   | The Pulse Modulator            | 11   | ŧŧ     | ft           |

| 3.2.13   | The Reference Oscillator       | 11   | 11     | tt .         |

|          |                                | (als | o ref  | er CD-232Y3) |

#### 3.2.1 Introduction

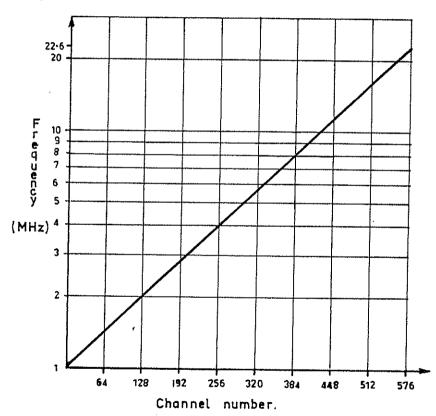

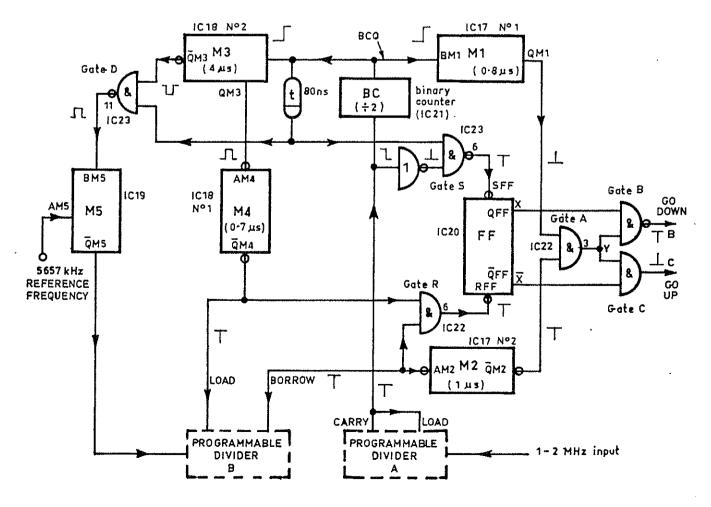

The Frequency Synthesizer provides the RECEIVER first conversion and TRANSMITTER drive frequencies which determine the operating frequency of the ionosonde. It generates 576 logarithmically spaced frequencies (or frequency channels) covering the range from 1MHz to 22.6 MHz. The Synthesizer is controlled by a 10-bit binary number derived from the OPERATIONAL DIVIDERS outputs (on A3All) which causes the Synthesizer to step through the 576 frequency channels during a sounding. As the channels are logarithmically spaced, a logarithmic frequency scale is provided for the ionogram. The relationship between the frequency channels and the channel number is illustrated in figure 3.2.1.

In addition, the synthesizer may be manually set to any of the 576 channels, for single frequency soundings, by setting a group of ten front panel switches.

The unit is located in the top rack assembly of the ionosonde immediately to the right of the PROGRAM unit A5. It is divided into two sections: the Digital section, A4Al and the RF section A4A2.

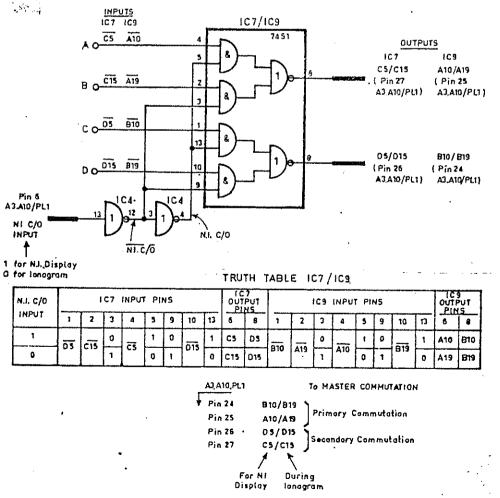

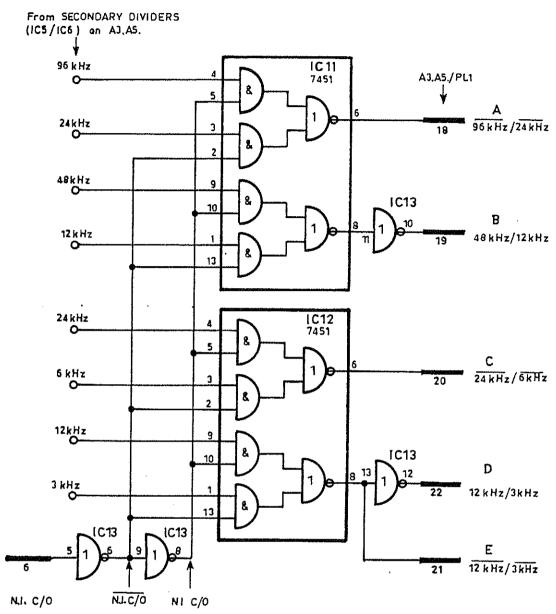

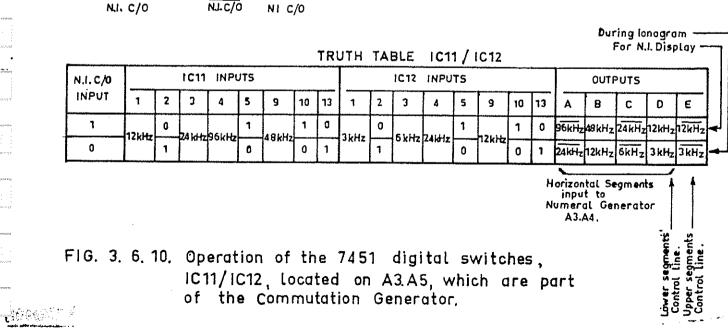

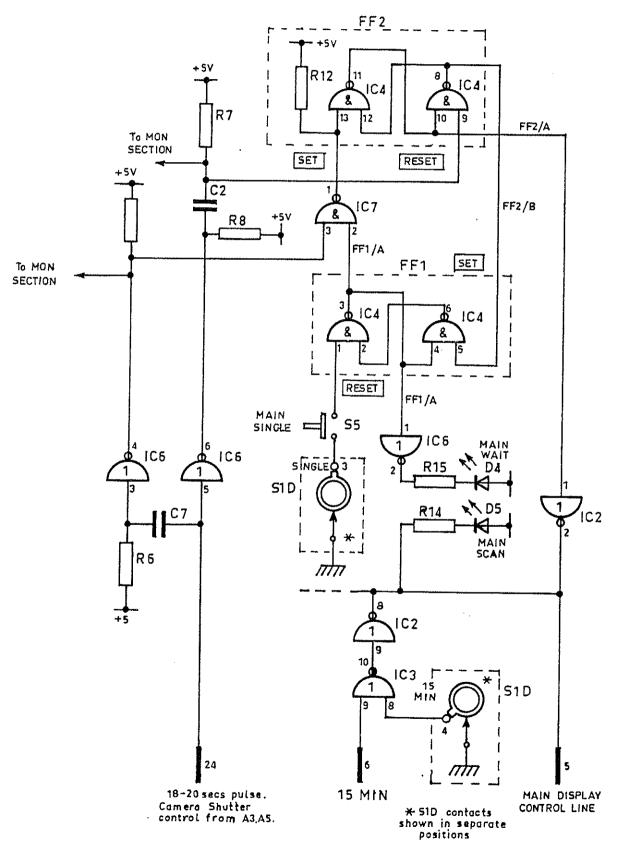

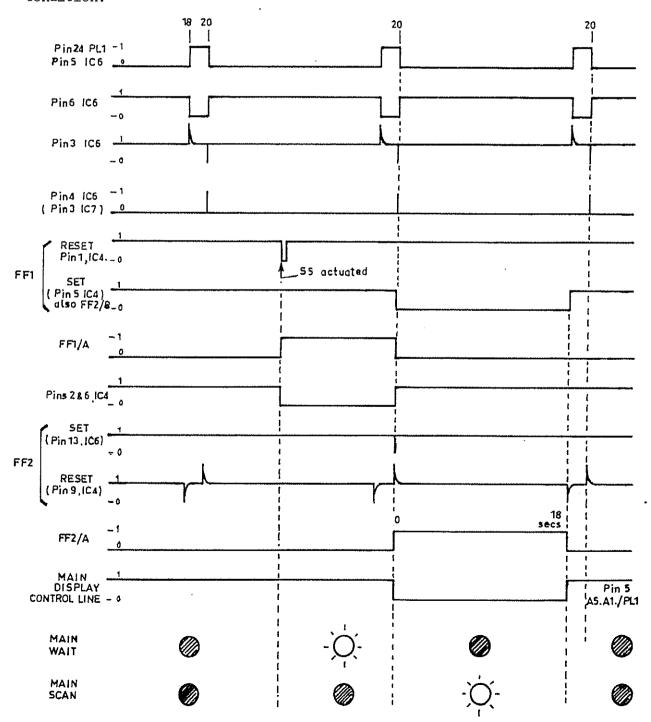

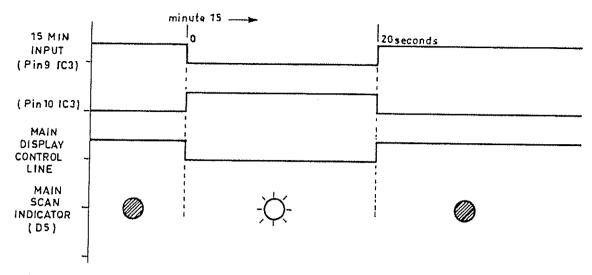

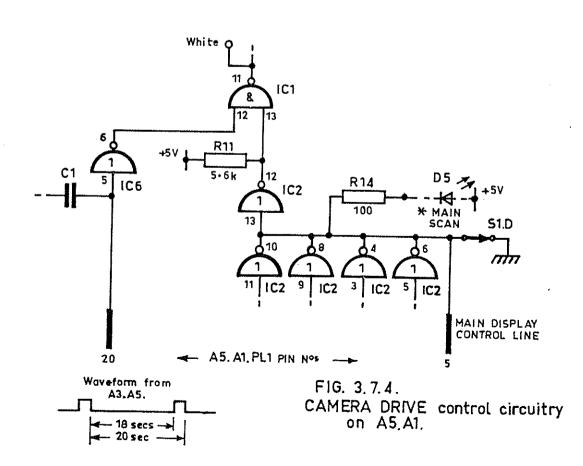

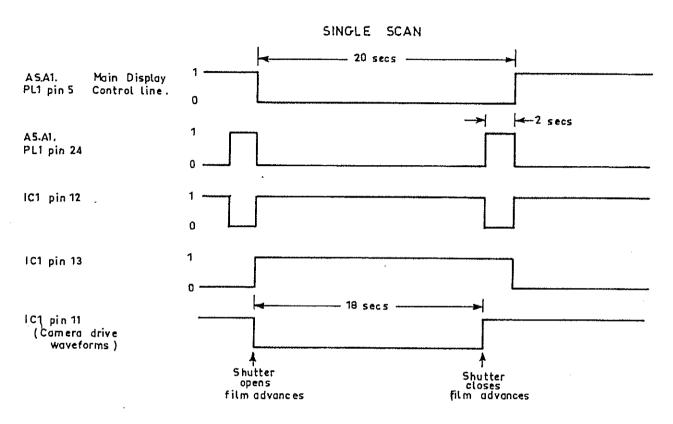

A block diagram of the Frequency Synthesizer is given in drawing CB-29Y1.